长期以来,FPGA的大部分市场份额被赛灵思(Xilinx)和英特尔(收购Altera之后)两家寡头占据。虽然也有其他厂商提供FPGA器件,但在世界范围内,尤其是高端FPGA领域扔难以撼动他们的地位。

Achronix就是一家提供FPGA技术和产品的厂商,他们自2004年成立以来一直在为FPGA的发展贡献创新的技术和产品。2013年,Achronix推出了基于当时英特尔最先进22nm工艺的高端独立FPGA器件Speedster22i。2016年,他们又推出了创新性的eFPGA,即嵌入式FPGA技术。eFPGA主要是为SoC设计公司授权IP,让客户在自己的芯片中嵌入FPGA单元。去年年底,Achronix对实现其eFPGA产品的更新换代,推出了性能更高、功耗更低、成本更低的eFPGA Gen4(第四代eFPGA IP)。

现在,Achronix又有了新想法:向高端独立FPGA领域继续发起冲击。最近,该公司宣布了一款高端FPGA器件,称作Speedster7t,采用多种先进设计思想和半导体工艺,针对高速增长的机器学习和数据加速应用。最近,Achronix Semiconductor总裁兼首席执行官Robert Blake先生来到北京,向我们介绍了该公司的这项最新技术。

首先,Speedster7t器件采用台积电(TSMC)的7nm FinFET工艺制造。我们知道,只有高端器件才会搭配高端工艺。Achronix的Speedster7t在三个方面实现了高端设计:高效计算力、高效大带宽的数据运送能力以及高效丰富的存储缓存能力。

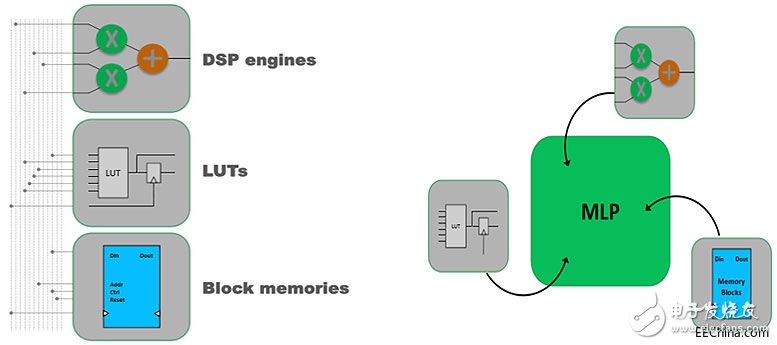

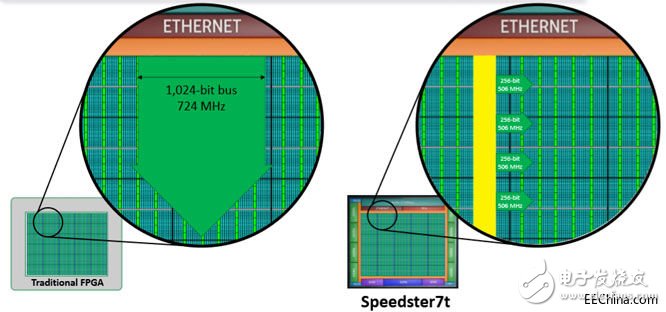

在计算能力方面,Speedster7t改变了传统的FPGA拓扑(下图左),而是将机器学习处理器(MLP)置于计算单元的核心(下图右),以实现最高计算性能和最高能效。

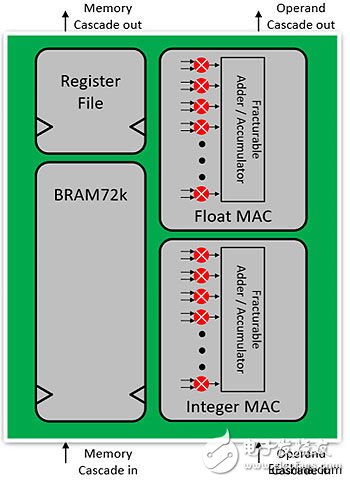

Speedster7t 的MLP采用了为人工智能和机器学习而优化了的数学功能块。如下图所示,该数学功能块拥有高密度乘法器阵列、紧耦合存储器块、 *** 作数和内存级联功能,并支持多种数字格式(定点和浮点)。Blake先生介绍说,定点的低位数运算更适合人工智能的矩阵乘法,而Speedster7t 的MLP采用了大量的4位定点整数运算单元。

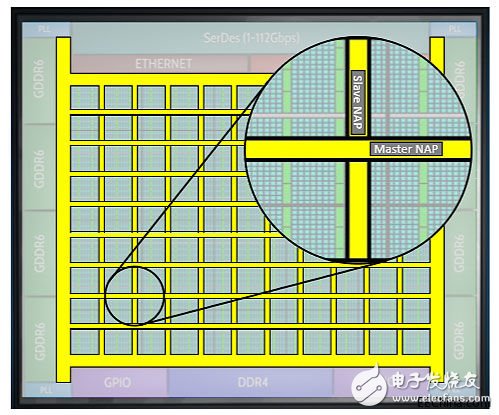

在芯片内部通信方面,Speedster7t采用了NOC(Network on Chip,片上网络)技术,实现了各个单元之间的高带宽连接,如PCIe到存储器以及逻辑功能块之间的高速互联,消除了传统FPGA布局布线的限制。

在以太网接口方面,Speedster7t采用了多通道布局,实现了400G的大带宽,突破了传统FPGA的带宽瓶颈。

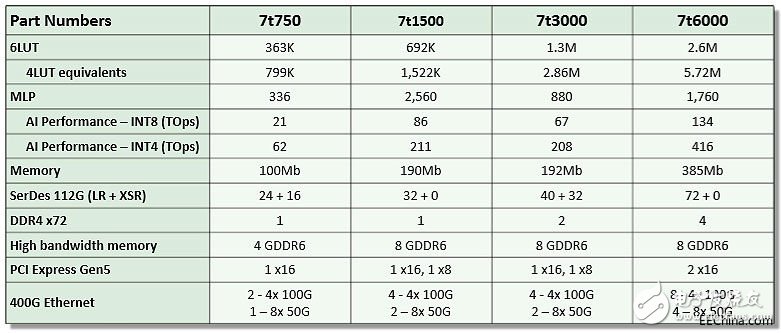

目前,Speedster7t系列公布了四款产品,如下图所示。器件的大小范围为从363K至2.6M 的6输入查找表(LUT)。支持所有Achronix产品的ACE设计工具现已可提供。第一批用于评估的器件和开发板将于2019年第四季度提供。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)