1.引言

随着电子技术的发展,在现代电子产品的故障检测中,往往需要频率和幅度都能自动调节的正弦信号源,并且要求该信号源产生的信号频率稳定性好,转换速度快,具有调频、调幅和调相的功能。本文结合实际需要,提出一种基于单片机和FPGA的直接频率数字合成器的设计方案,能够产生两路频率和相位均可调的正弦波信号,达到了预定的要求。

2.系统方案设计

2.1 系统的性能分析

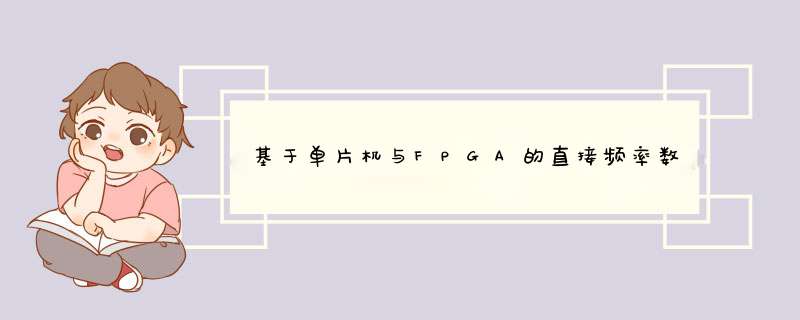

系统主要由单片机最小系统、存储器电路、FPGA模块、键盘与显示接口电路、D/A转换电路、低通滤波电路组成,其硬件框图如图1所示。通过键盘输入频率控制字、相位控制字和幅值控制字,单片机最小系统控制FPGA模块产生用户需要的正弦波信号,再经过DA转换,最后通过低通滤波器生成平滑的正弦波信号。

系统的性能要求:频率范围20Hz~20KHZ,步进20Hz;差0o~359o,步进1o;两路输出正弦波信号,峰峰值分别在0.3V~5V变化;数字显示频率、相位差。

2.2 系统实现的原理

2.2.1 DDS的基本原理

直接数字频率合成器(DDFS)的基本原理:

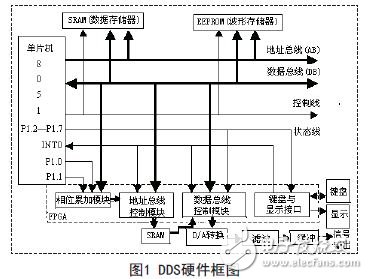

DDS是利用采样定理,根据相位间隔对正弦信号进行取样、量化、编码,然后储存在EPROM中构成一个正弦查询表,通过查表法产生波形。

它是由参考时钟、相位累加器、正弦查询表和D/A转换器组成,如图2所示。

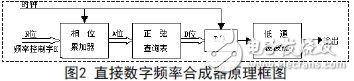

相位累加器由N位加法器与N位累加寄存器级联构成,其原理框图如图3所示。每来一个时钟脉冲Fc,N位加法器将频率控制数据K与累加寄存器输出的累加相位数据相加,把相加后的结果Y送至累加寄存器的输入端。累加寄存器一方面将在上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,以使加法器在下一时钟的作用下继续与频率控制数据K相加;另一方面以相加后的结果形成正弦查询表的地址,取出表中与该相位对应的单元中的幅度量化正弦函数值,作为取样地址值送入幅度/相位转换电路。这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。

相位累加器的最大计数长度与正弦查询表中所存储的相位分隔点数相同,在取样频率(由参考时钟频率决定)不变的情况下,由于相位累加器的相位增量不同,将导致一周期内的取样点数不同,输出信号的频率也相应变化。

如果设定累加器的初始相位,则可以对输出信号进行相位控制。由采样原理可知,如果使用两个相同的频率合成器,并使其参考时钟相同,同时设定相同的频率控制字、不同的初始相位,那么在原理上就可以实现输出两路具有一定相位差的同频信号。

2.2.2 FPGA实现的直接数字频率合成器

基于DDS的基本原理,利用Altera公司的FPGA芯片FLEX10系列器件设法将波形采样点的值依次通过数模转换器(MDAC)转换成模拟量输出,可达到预期的目的,具有较高的性价比。其基本环节由计数器(Counter)、只读存储器(EPROM)、数模转换器(MDAC)和滤波器等组成。

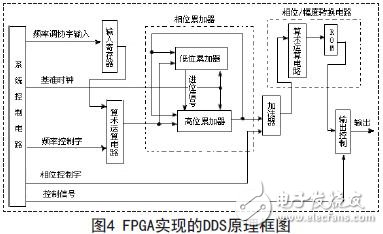

具体方案如下:累加器由加法器和D触发器级联组成,在时钟脉冲fc的控制下,对输入频率控制字K进行累加,累加满量时产生溢出。相位累加器的输出对应于该合成周期信号的相位,并且这个相位是周期性的,在0~2π 范围内起变化。相位累加器位数为N,最大输出为2N-1,对应于2π的相位,累加一次就输出一个相应的相位码,通过查表得到正弦信号的幅度,然后经D/A转换及低通滤波器滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。整个DDS电路的电路结构如图4所示。

3.系统硬件电路设计

在功能上,单片机与FPGA有很强的互补性。

单片机具有性价比高、功能灵活、易于人机对话、良好的数据处理能力等特点;FPGA则具有高速、高可靠性以及开发便捷、规范等优点。用这两类器件相结合的电路结构在许多高性能仪器仪表和电子产品中仍将被广泛应用。

单片机的功能主要是传送频率控制字K1和相位控制字K2给FPGA处理;生成波形表存储于EEPROM中;控制键盘的写入和LED的显示;控制DAC0832进行幅值转换。在每次加电前都要通过单片机初始化,将写好的程序加载在信号产生系统上,然后把从键盘上输入的数据送到中央处理芯片上,信号通过低通滤波器输出的同时,LED数码管显示信号的频率和相位差。

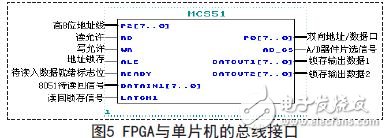

FPGA与单片机的总线接口如图5所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)