51数据存储器的扩展

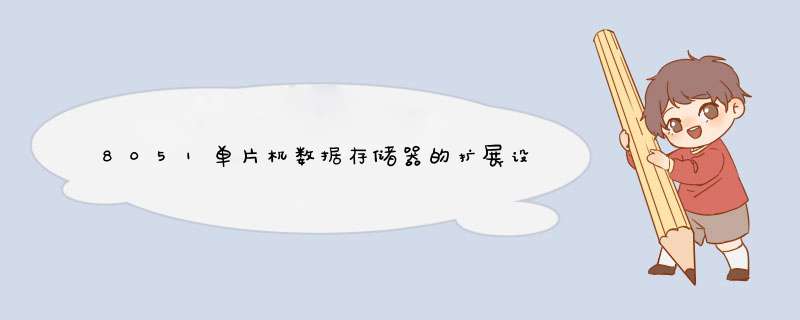

A0-A12为地址线,总共13条,则该存储器的物理存储空间有2的13次方,即8K。

D0-D7为数据总线,共8条,即该存储器的每个存储单元有8位数据,即通常所说的字节为8,又叫一个字节 。

CS为片选信号,当该信号为0时,存储器才能正常读写,当CS为1时,存储器的输出端D0-D7和地址总线A0-A12都为高阻状态,即相当于存储器芯片没有接入电路,片选信号常用与电路中有多片同类芯片时选择哪一个芯片有效,即哪一片芯片被接入电路中,在本例中,由于只有一片程序存储器,没有选择的必要,所以可把片选端接地,使其永远有效。

RD为数据存储器输出运行端,即通常所说的存储器读信号,应该信号有效即RD=1而且无效时,由地址决定的数据存储器的某一个单元中的数据输出到总线上,存储器与数据总线断开。

WR为数据存储器输入允许端,即通常所说的存储器写信号无效时,数据总线输入由地址线决定的数据存储器的某一个单元中当该信号为1且RD信号也为1时,存储器与数据总线断开。

VCC为存储器的电源输入端,Vss为存储器的电源接地输入端。

G为地址锁存器74373的锁存信号输入端,当该信号为0时,74373的输出端与输入端断开,输出端保持上次输入的数据不变,当该信号为1时,74373的输出端与输入端接通,输出端信号随输入端的变化而变化,对8051来说,P0输出经74373锁存后为低8位地址总线,P2口为高8位地址总线,共16条地址线,所以8051能访问的存储器单元数为2的16次方,即64K称为8051的逻辑地址空间,地址从0000H-OFFFFH。

存储器有13条地址线,所以对存储器来说,实际的存储单元只有2的13次方,即8K个,其地址从0000H-1FFFH,称为存储器的物理地址 。在本例中,由于存储器的片选段接地,没有占有CPU的地址线,所以CPU的64K逻辑单元地址平均分配给8K单元的物理存储器,即每一位物理存储器单元拥有8个逻辑地址,比如要访问物理存储器的00单元,要求存储器的地址引脚A0-A12上全为0,本系统中的CPU的地址线A0-A12恰好与存储器的A0-A12对接,所以只要逻辑地址中的低13位为0,就能选中存储器的物理地址00单元,而CPU的地址线A13,A14,A15悬空。

显然,这三位悬空线的8种不同组合决定了该物理存储器单元有8个逻辑单元,第一个逻辑单元为0000H,第二个逻辑单元为2000H,第三个逻辑单元为4000H,第四个逻辑单元为6000H,第五个逻辑单元为8000H,第六个逻辑单元为0A000H,第七个逻辑单元为0C000H,第八个逻辑单元为0E000H。

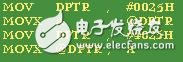

下面我们举例说明本系统中对外部数据存储器的访问过程,假定8051的EA引脚接高电平,即8051使用片内程序存储器,下面是这个程序片断每条指令的意义:

第一条指令给寄存器DPTR赋初值0025H

第二条指令讲外部数据存储器OO25H单元的内容送入累加器A

第三条指令对寄存器DPTR赋初值2025H

第四指令将累加器的内容送外部数据存储器4025H单元,假定当前PC的内容为0050H,并假定外部数据存储器0025H单元为12H:从内部程序存储器中取第一指令并运行,结果为给寄存器DPTR赋初值0025H,取第二指令,执行第二指令。

第二指令执行过程为:发控制信号使P0口,P2口的控制端为1,将DPTR内容送内部地址总线,低8位地址进入P0口,再经数据选择开关出现在P0口的8条引脚上,高8位地址到达P2口引脚上。

同时,CPU使ALE引脚为高电平,74373导通,低8位地址出现在74373的输出端,待地址稳定后,使ALE变为低 电平,74373输出端与输入端断开,即锁存。此后,74373的输出端一直保持低8位地址不变,直到下次ALE引脚出现高电平为止,CPU使P0口的地址/数据全部为1。则上拉场效应管导通,下拉场效应管截止,这样,才能读回外部数据总线上的数据。

否则,若下拉场效应管导通,P0口引脚被下拉场效应管接地,则从外部数据总线上读回的数据永远为0,CPU使PSEN引脚为低 电平,存储器的输出允许信号RD有效,即0025H单元的内容12H送数据总线,结果为给寄存器DPTR赋初值4025H。

然后是执行第四条指令,下面我们看看第四条指令的执行过程,CPU使P0口和P2口的控制端C为1,将DPTR的内容4025H送内部地址总线,高8位40H地址40H出现在P2口引脚上,低8位地址25H出现在P0引脚上,ALE变为高 电平,低8位地址出现在74373的输出端,ALE变为低电平,低8位地址被锁存,CPU将累加器A中内容12H送P0口,WR变成低电平,存储器数据总线上的数据12H送入地址总线指定的物理单元0025H中。

来源;21ic

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)