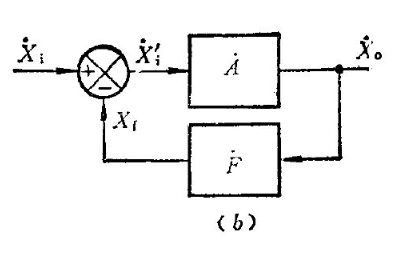

闭环增益G=A/(1+FA)。 其中A为开环增益,F为反馈系数,AF为环路增益

A(开环增益) = Xo/Xi

F(反馈系数)=Xf/Xo

运放震荡自激的原因:

1、环路增益大于1 (|AF|》1)

2、反馈前后信号的相位差在360度以上,也就是能够形成正反馈。

参考《自控原理》和《基于运算放大器和模拟集成电路的电路设计》

在负反馈电路时,反馈系数F越小越可能不产生自激震荡。换句话说,F越大(即反馈量越大),产生自激震荡的可能性越大。对于电阻反馈网络,F的最大值是1。如果一个放大电路在F=1时没有产生自激振荡,那么对于其他的电阻反馈电路也不会产生自激振荡。F=1的典型电路就是电压跟随电路。所以在工作中,常常将运放接成跟随器的形式进行测试,若无自激再接入实际电路中

自激振荡的引起,主要是因为集成运算放大器内部是由多级直流放大器所组成,由于每级放大器的输出及后一级放大器的输入都存在输出阻抗和输入阻抗及分布电容,这样在级间都存在R-C相移网络,当信号每通过一级R-C网络后,就要产生一个附加相移。此外,在运放的外部偏置电阻和运放输入电容,运放输出电阻和容性负载反馈电容,以及多级运放通过电源的公共内阻,甚至电源线上的分布电感,接地不良等耦合,都可形成附加相移。结果,运放输出的信号,通过负反馈回路再叠加增到180度的附加相移,且若反馈量足够大,终将使负反馈转变成正反馈,从而引起振荡。

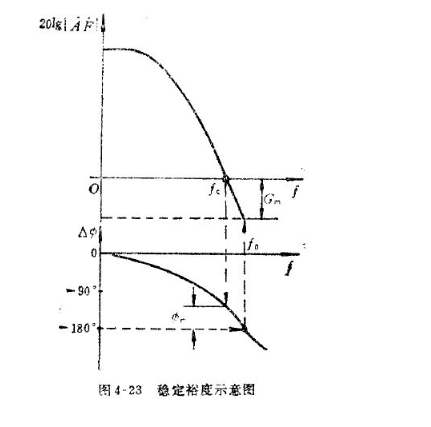

重要的概念

相位裕度 ---如下图所示,显然我们比较关心当20lg|AF|=0时,相位偏移是否超过180

运放震荡原因:

1. 可能运放是分布电容和电感引起的 ----------------可通过反馈端并联电容,抵消影响。

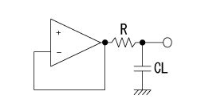

2. 运放驱动容性负载导致。 ---------------------------可在运放输出端先接入一个电阻,再接负载。

3. 可能是反馈过深引起的 -----------------------------可通过减少环路增益,减少反馈量,即增大闭环增益。例如运放作为电压跟随易震荡,增大放大倍数,震荡会消失。

解决方法:

1. 环内补偿

运放反馈电阻并接反馈电容:----相位超前补偿

(如下图显然补偿后0dB的频率后移,运放带宽扩大,即自激的频率点后移了)

小电容叫做移相电容,防止运放自激的一般取0点几皮法到几十皮法几百皮法,看工作的频率以及运放的型号来定

简单点说加的电容越大,带宽越窄

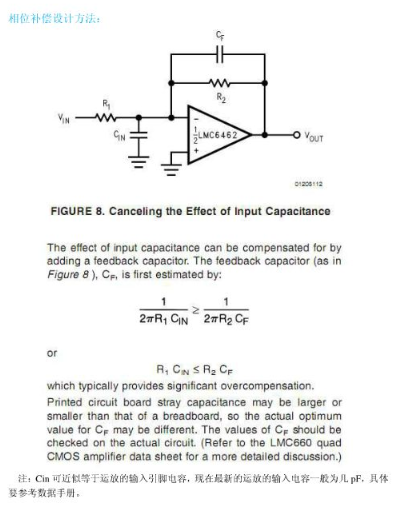

防止振荡Rf和运放的输入电容及杂散电容形成极点,如果该极点在运放使用的频率范围内就可能使运放产生振荡;加入Cf后,Cf和Rf产生零点,用来抵消极点。一般取值Cf》Ci,Ci为运放的输入电容和输入脚杂散总电容。

2. 环路外补偿法、

在运放的输出端串上一个小电阻

再连到后级,十几欧到几十欧之间既可,具体值与后级电路的输入电容有关,可尝试不同的电阻值,获得稳定的输出

由于考虑到负载存在一点的容性(CL),环路增益在输出电阻和CL的作用下降低。同时,相位和增益之间不再有比例关系,相位滞后成为决定性因素,使反馈环路失去稳定,最糟糕时可能导致震荡。。因此在运放输出端接入一个小电阻R,消除因CL而产生的反馈环路相位滞后

PS:

1.电源供电稳定,最好并联0.1uf ,10uf等电容

2.放大倍数不能过大,放大级数也不要超过四级

实验或测试之前,若用示波器接在运放输出端,有时可以看到频率较高且近似正弦波的波形,偶尔也出现低频振荡的情况。可根据产生振荡的原理采取不同的方法解决:

(1)反馈极性是否接错或负反馈太强。若将负反馈错接成正反馈则极易产生振荡。另外,负反馈愈强也愈易产生自激。

(2)若输出端接有的电容性负载,由于容性负载加强了电路的相移,所以更易自激。可以用另一个RC环节来补偿相移,如果补偿得好自激振荡就会消除。

(3)接线杂散电容过大。当输人回路为高阻时,由接线到地或接线之间的杂散电容与电阻组成的滞后环节,将使组件变得不稳定。为此可在Rf(反馈电阻)两端并联一个电容CF,或者在运放的输人端并联一个RC支路,这两个环节都属于超前校正的性质,即它们产生的相位超前作用将有可能抵消前面所述杂散电容所起的相位滞后作用,从而使运放稳定。

(4)电源接线旁路措施不够。电源引线不仅具有一定电阻,还有一定的电感和分布电容,因此当有许多运放接到同一根电源线时,,将通过这些因素产生相互之间的影响,解决的办法是在印刷电路板插座上的正负电源的接线端与地之间接上几十uF的电解电容和0.01uF的陶瓷电容相并联,如果运放是作为宽频放大,须选用低电感量的电容。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)