3.最基本的DSP资源

3.1 由FIR滤波器谈起

随着各种应用复杂度的不断提升,传统的DSP和处理器的架构无法支持这么复杂的并行数据算法的需求。FPGA却恰好能够满足这样的需求。FPGA拥有大量的DSP计算单元能够帮助用户实现各种各样的复杂算法。拿FIR滤波器举个例子。

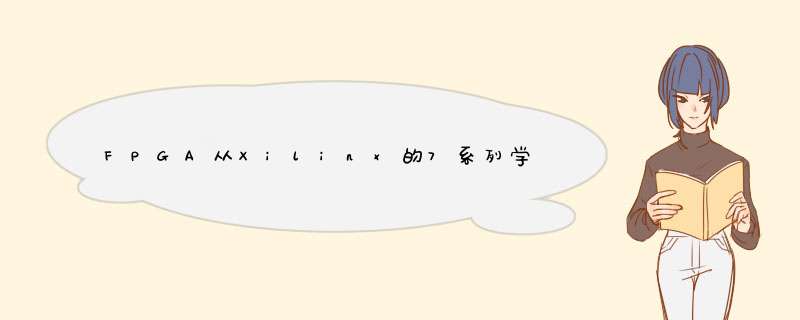

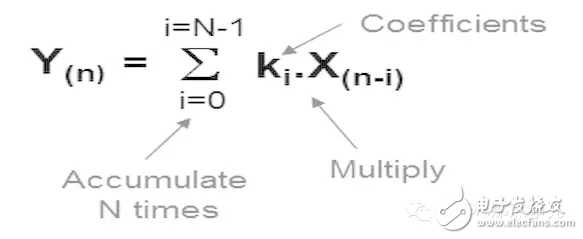

如上图所示,这是一个典型的FIR滤波器,第一个图是FIR滤波器的公式,第二个图是FIR滤波器的一个框图。可以看到,FIR滤波器是线性时不变系统的卷积和公式。传统上,一个FIR滤波器被画成一组并行乘法,并且所有馈送结果到单个加法器的架构。这个加法器通常被实现为一个加法器树,并且使用流水线以提高其性能。这种做法实现FIR过滤器是最简单的,但它不是唯一可能实现方法。下面将比较一下传统DSP或者处理器的顺序处理和FPGA并行处理两种方法。

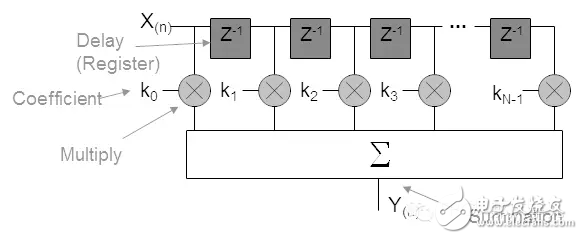

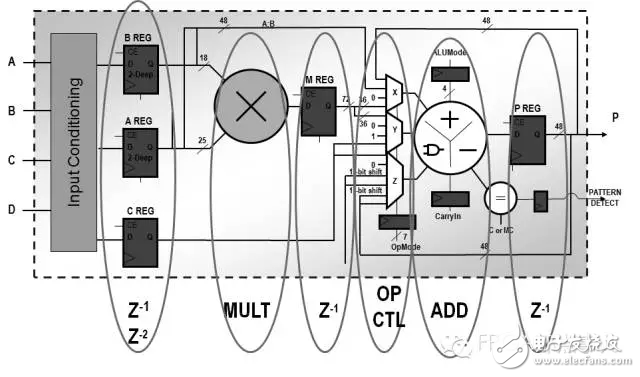

在左边的传统DSP处理的方式上,它只有一个乘法器和加法器,只能通过数据、系数和所需要的时间去循环产生一个结果。这个处理过程将会非常慢,因为它要依靠乘法器和累加器的所需要调用的次数来产生一个结果。如上边左图所示,一个3960抽头的FIR滤波器运行在一个1.2GHz的DSP处理器上,那么它只能有303KSPS的能力。这个级别就很低了,只有K级。那么在右边的FPGA的处理方式,相当数量DSP的处理单元能够同时进行所有的乘法 *** 作,每个时钟都能够产生一个结果。这个3960个抽头的FIR滤波器可以恰好放在一个包含了3960个DSP单元的Virtex-7 XT的芯片中。尽管处理的频率也就是DSP处理器的1/2,但是增加的并行处理能力能够是FIR滤波器能够达到600多MSPS的能力。虽然上图上最后所有乘法器的数据被同时送到了加法器的处理单元。实际上,这是需要一个流水线的加法器来最终产生想要的结果。实际上7系列的DSP单元包括了输入调整,流水线寄存器,专用的乘法器, *** 作控制单元,专用的加法器和级联路径。

输入调整包括预加器和输入流水线寄存器。流水线寄存器,在这个图中标记为Z-1和Z-2在几个地方,在DSP的单元内最大限度地提高性能。乘法器和加法器是在DSP片的主要组成部分。 *** 作控制寄存器和专用多路复用器可以在一个DSP单元内选择不同的 *** 作命令,从而增加了可编程性和灵活性。输入和输出级联路径(上图并未表示),允许通过使用专用和快速布线资源将多个DSP的单元被链接在一起,以形成更广泛和更复杂的功能。下次将讲述是如何在DSP单元中使用FIR滤波器可以使用DSP片结构来实现的示例。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)