2016开源硬件与全可编程技术论坛暨Xilinx中国大学合作十周年庆典于今天在上海召开。本活动由Xilinx公司与上海交通大学共同主办,将有200多位专家学者分享技术趋势和业界动态,研讨科研和教学经验。活动将成为国内全可编程技术的一次盛会。以下是赛灵思CTO Ivo Bolsens先生带来的主题演讲内容:

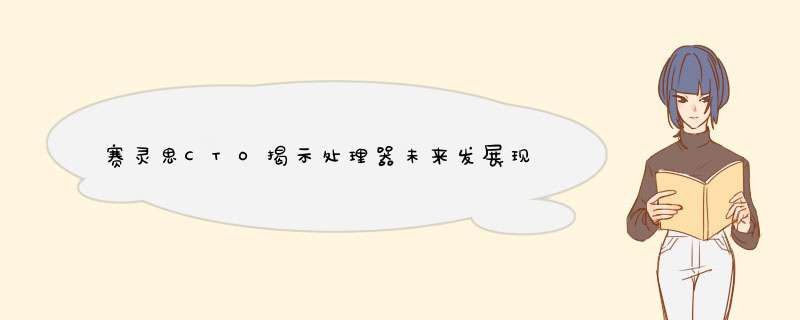

高级工艺产品增长惊人

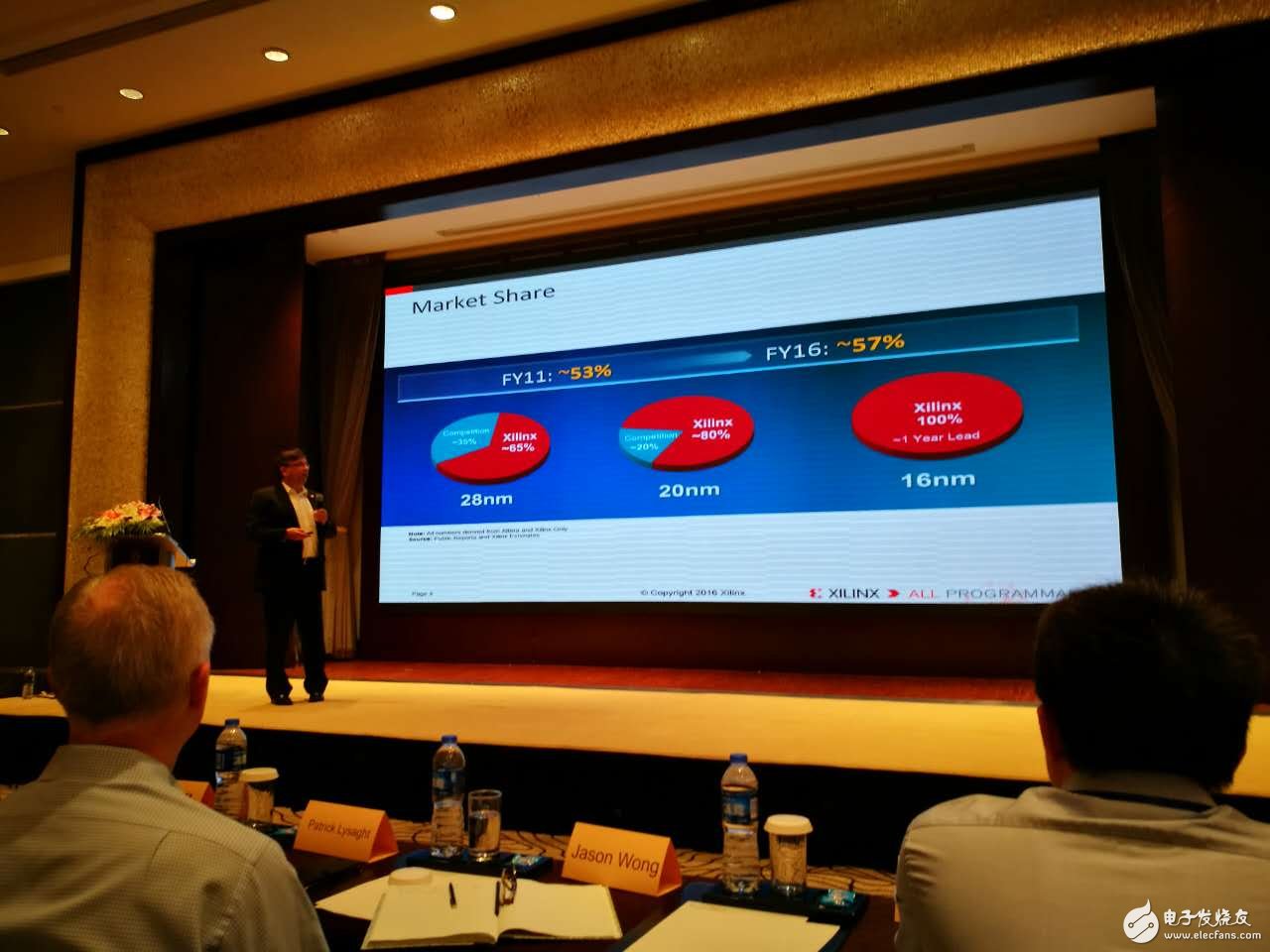

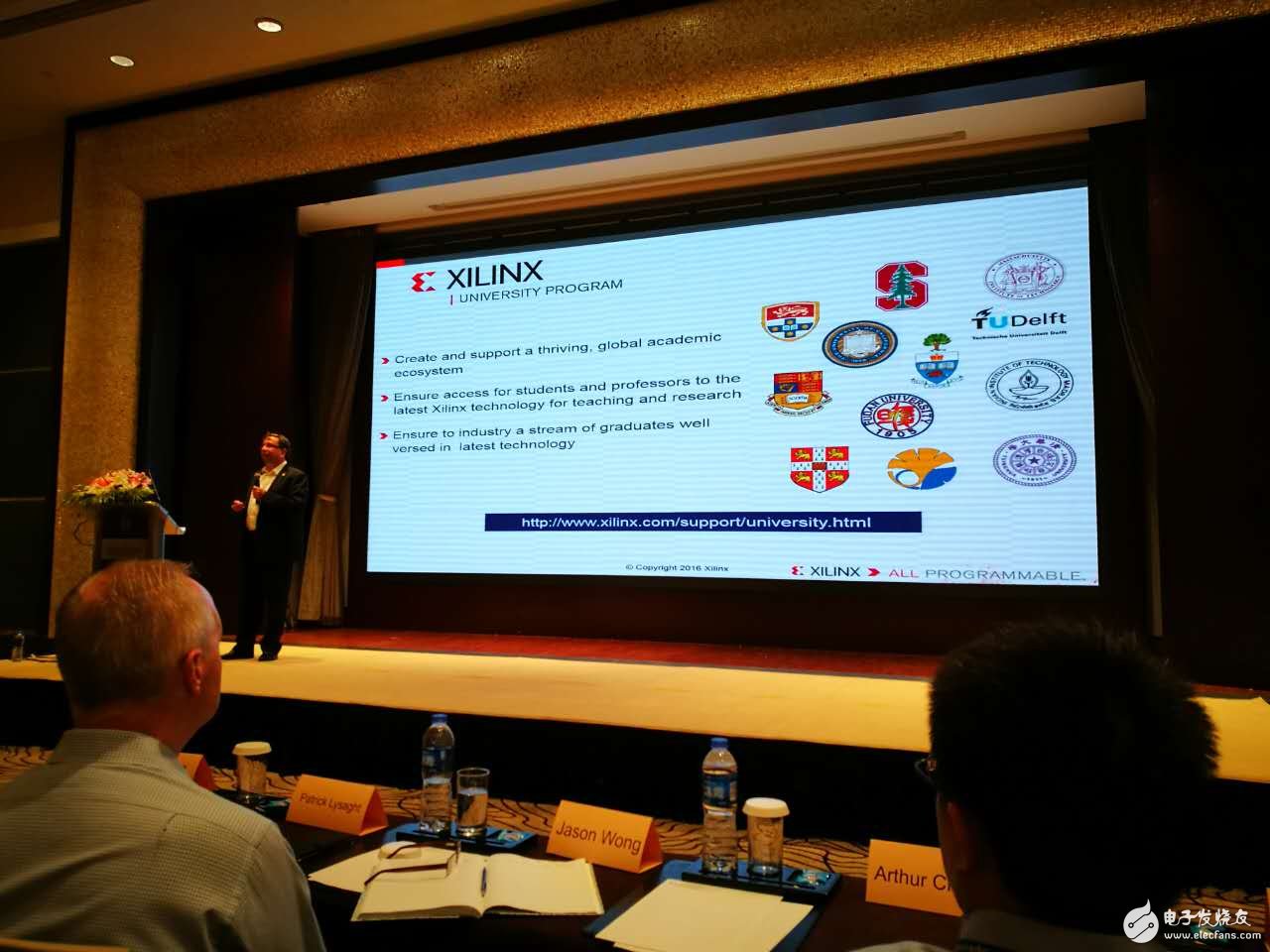

赛灵思全球大学计划去年培养了超过1000名教授,全球超过70%的高校使用赛灵思的技术

赛灵思全球大学计划1

赛灵思全球大学计划2

全球超过70%的高校使用赛灵思的技术

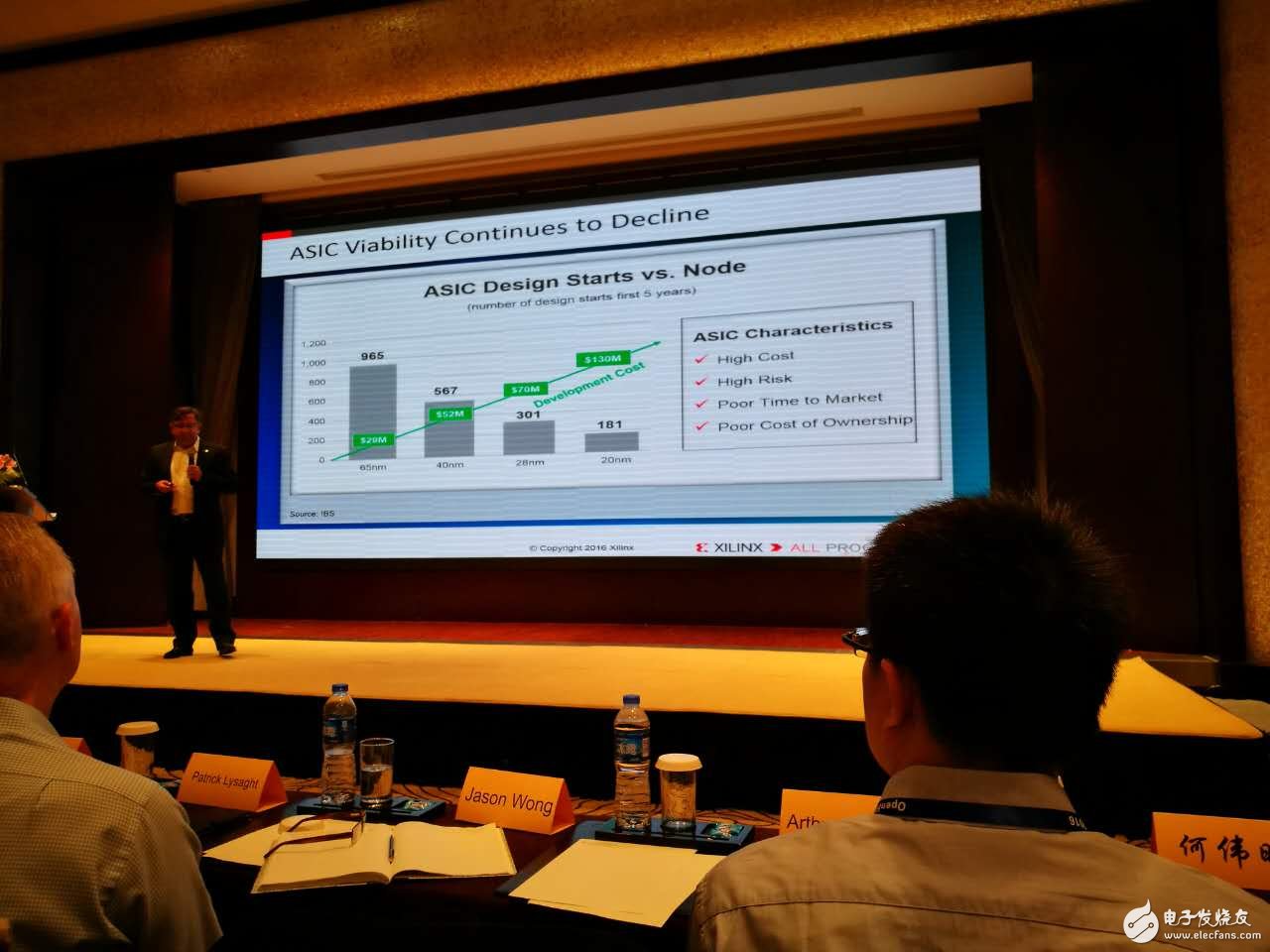

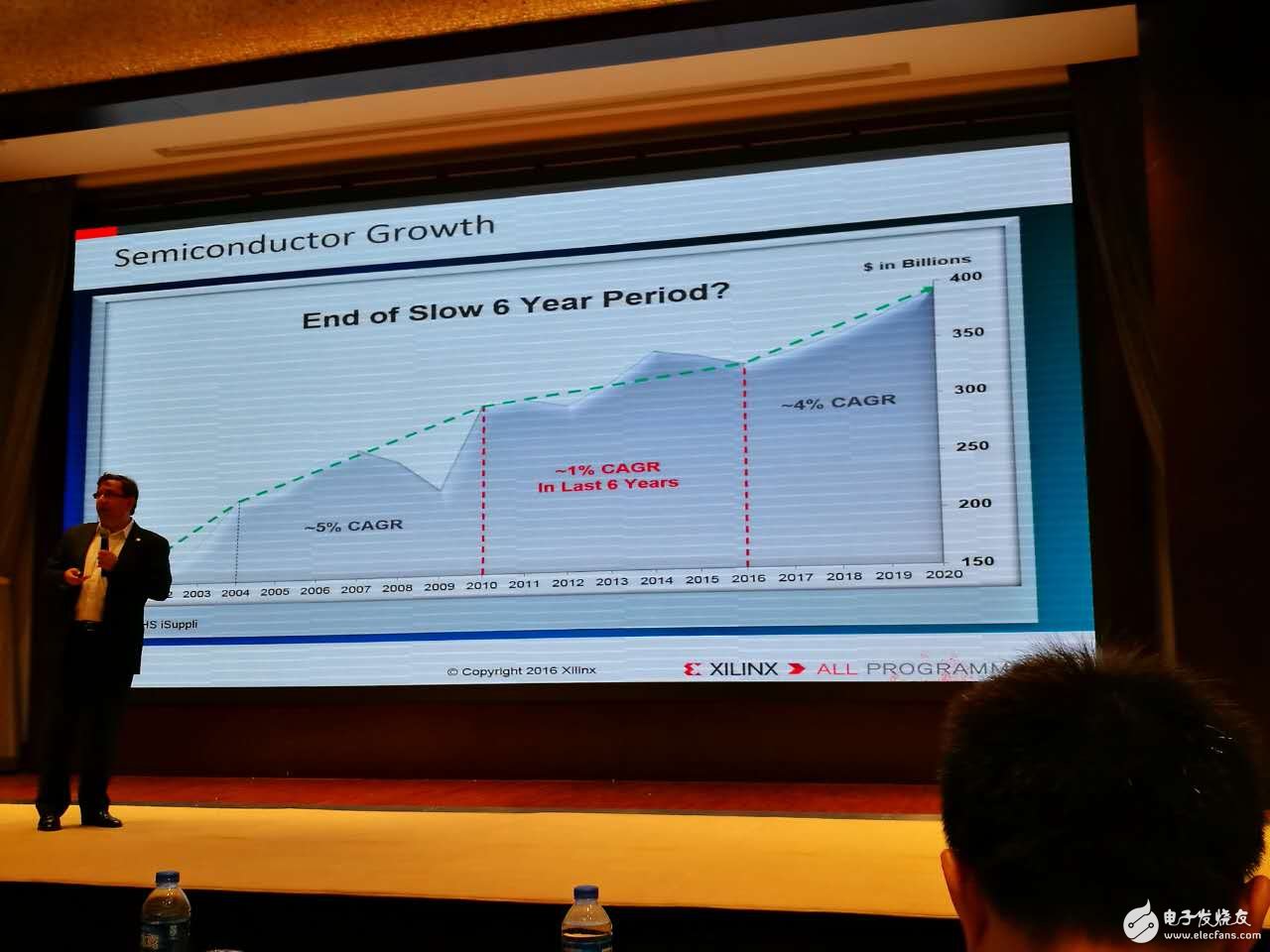

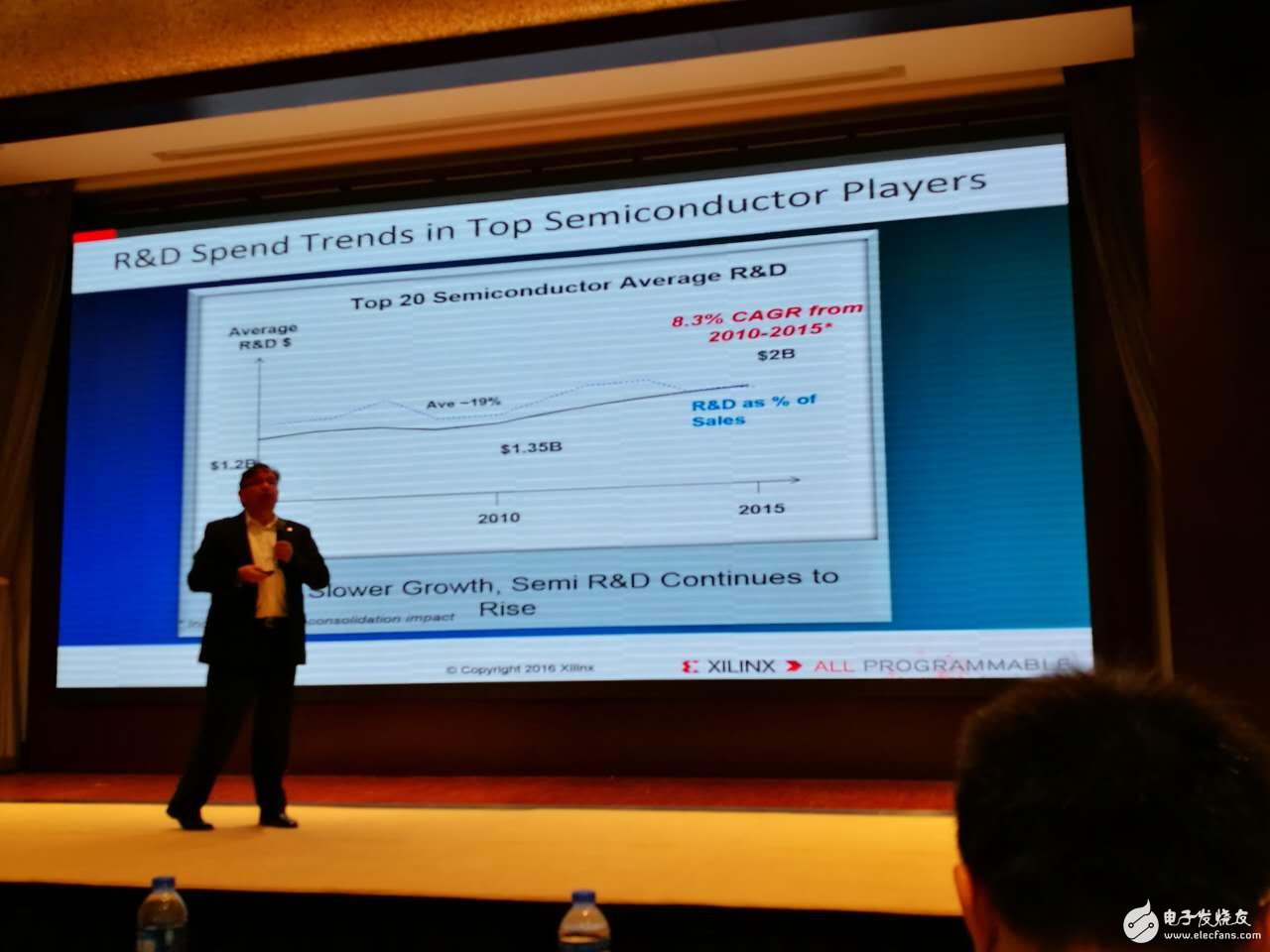

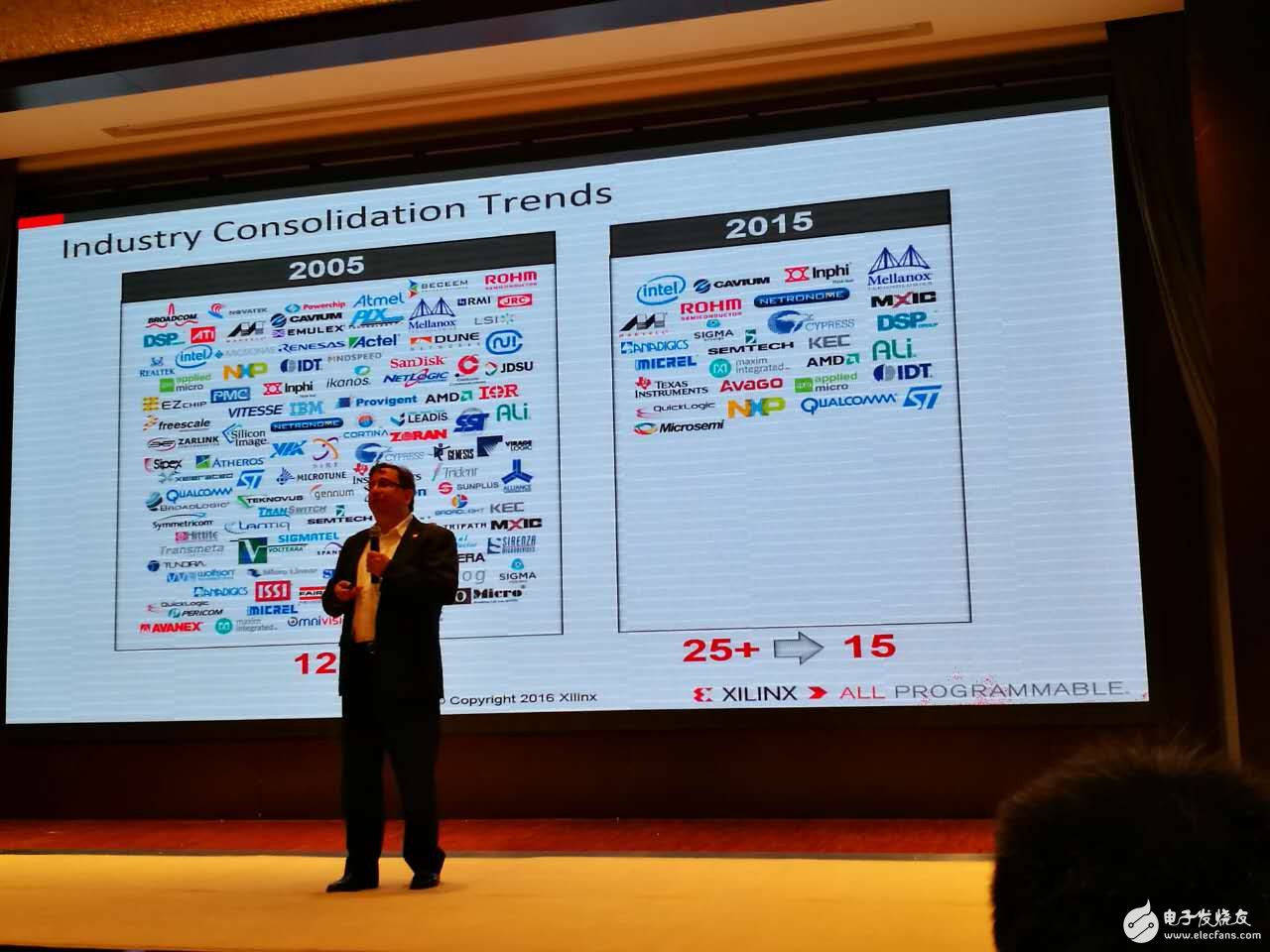

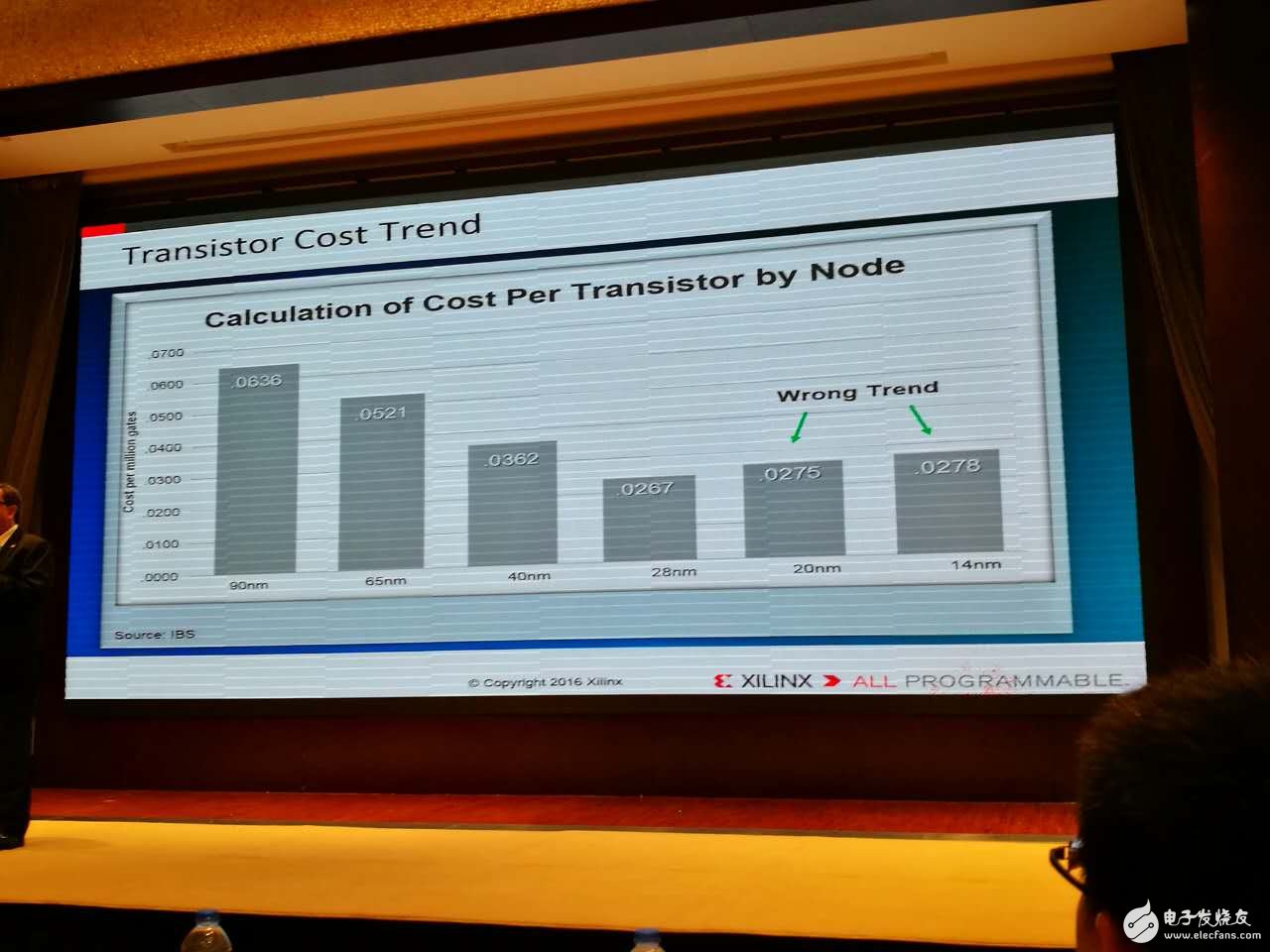

随着工艺成本提升,过去5年ASIC设计数量出现大量下降,半导体支出增加,合并加剧,平均每晶体管的成本不再降低了。

半导体支出增加

合并加剧

平均每晶体管的成本不再降低了

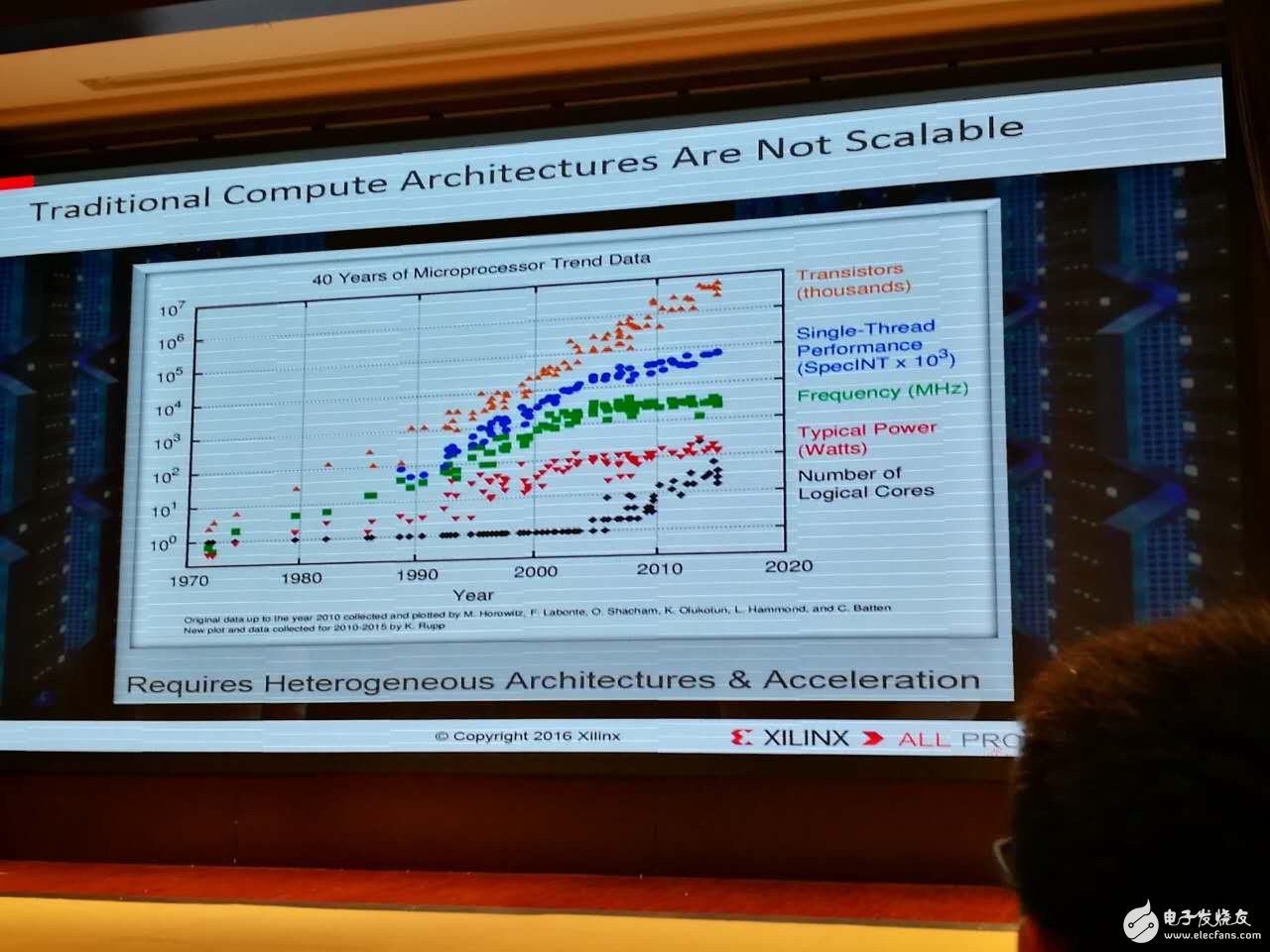

过去40年处理器发展大数据

异构兴起

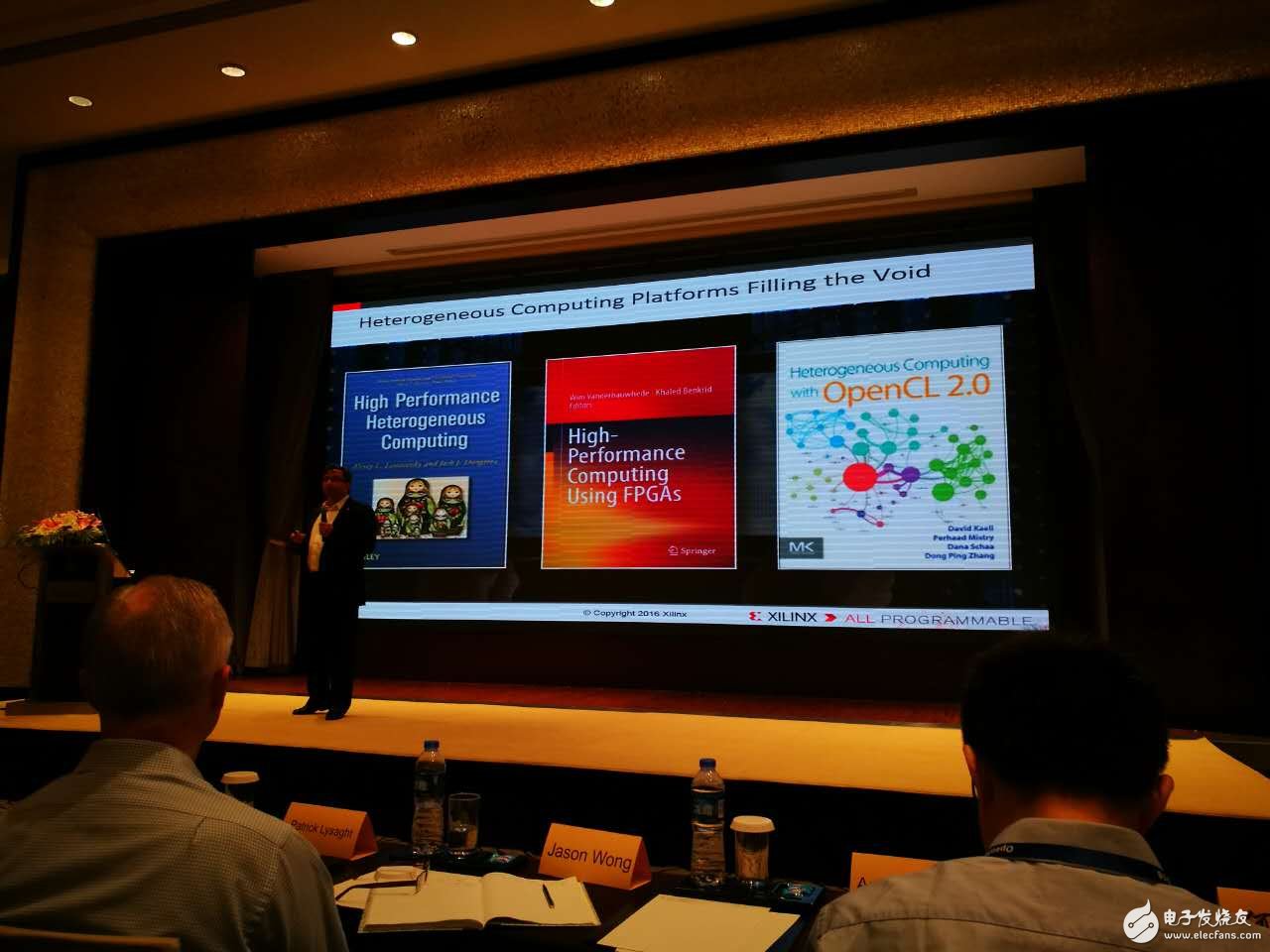

FOGA架构发展趋势

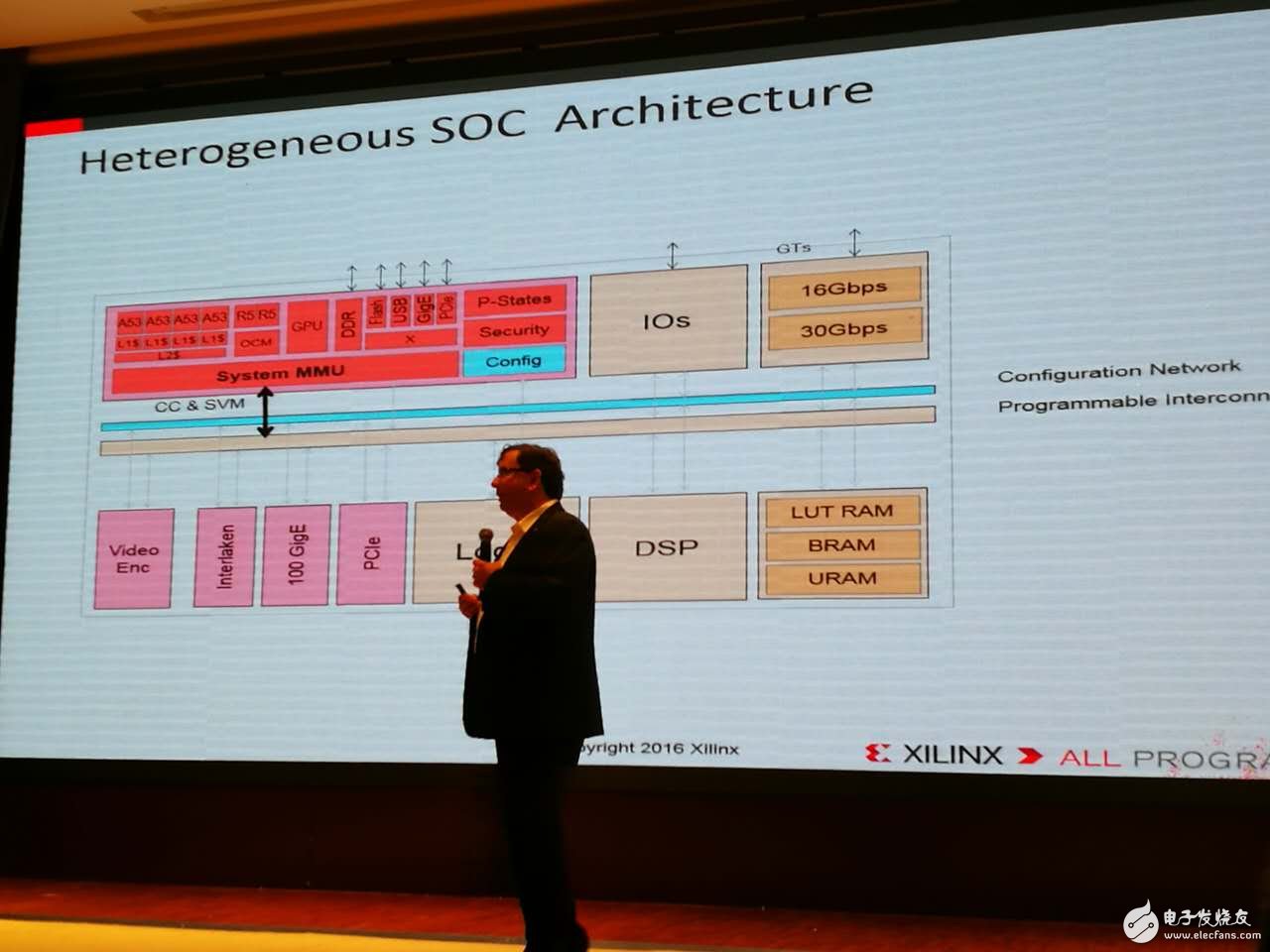

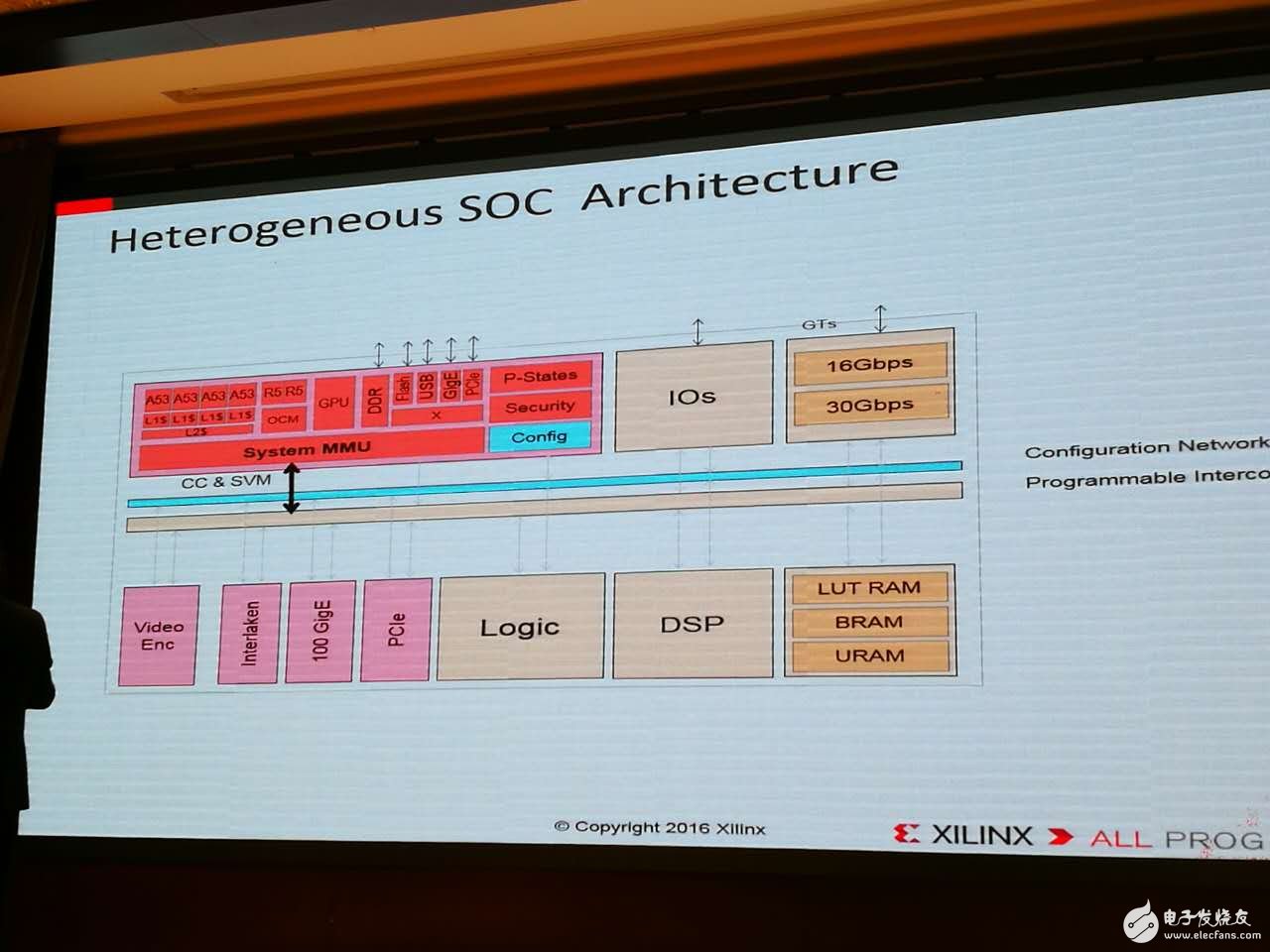

下图是异构SOC架构,可配置网络可编程、互联

异构SOC架构1

异构SOC架构2

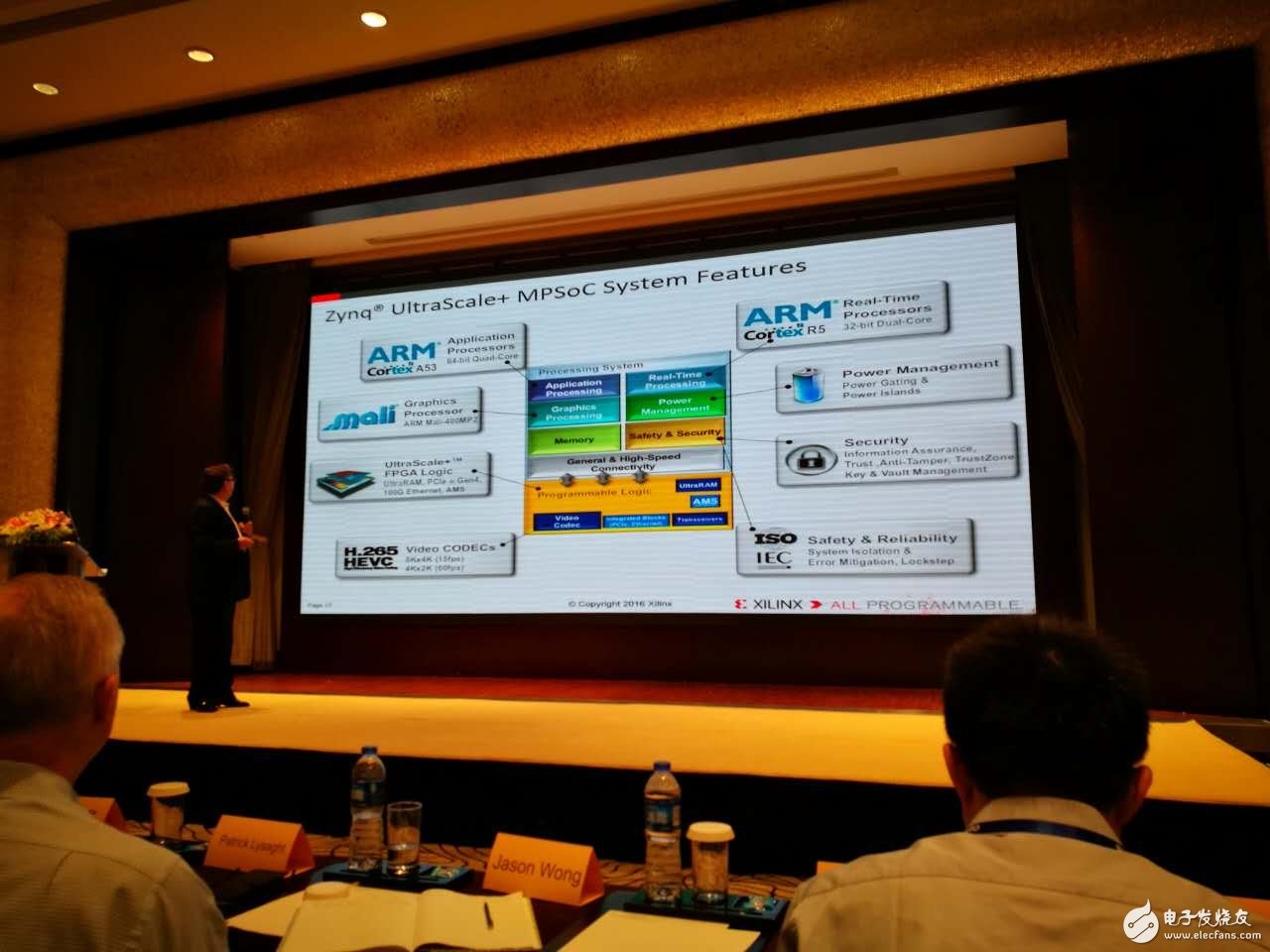

Zynq UltraScale+ MPSoC器件提供64位处理器可扩展能力,将实时控制系统与软件和硬件引擎相结合,完成显示、视频、波形生成以及数据包处理等 *** 作。基于通用的实时处理器与可编程逻辑组合结构,主要分为三款不同的异构组合系列:集成双核应用处理器的CG系列、集成四核应用处理器和GPU的EG系列以及在EG系列上额外增加视频编解码模块的EV系列。为各类应用创造了无线的可能性,如5G无线应用、下一代ADAS系统、工业物联网系统等。

MPSOC介绍

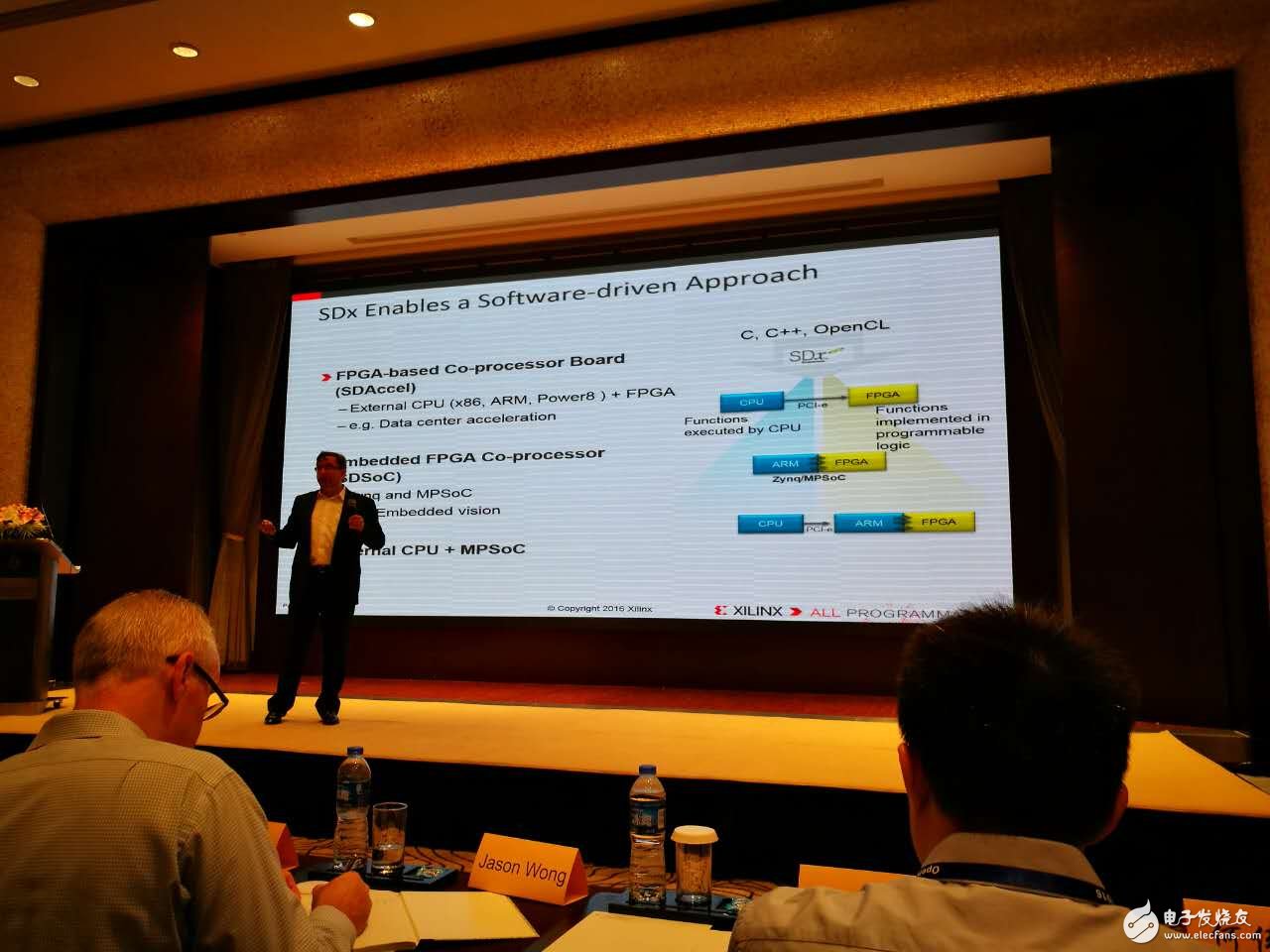

从软件层面看FPGA,向着提供全软件体验发展

从软件层面看FPGA

赛灵思在高增长市场的角色:

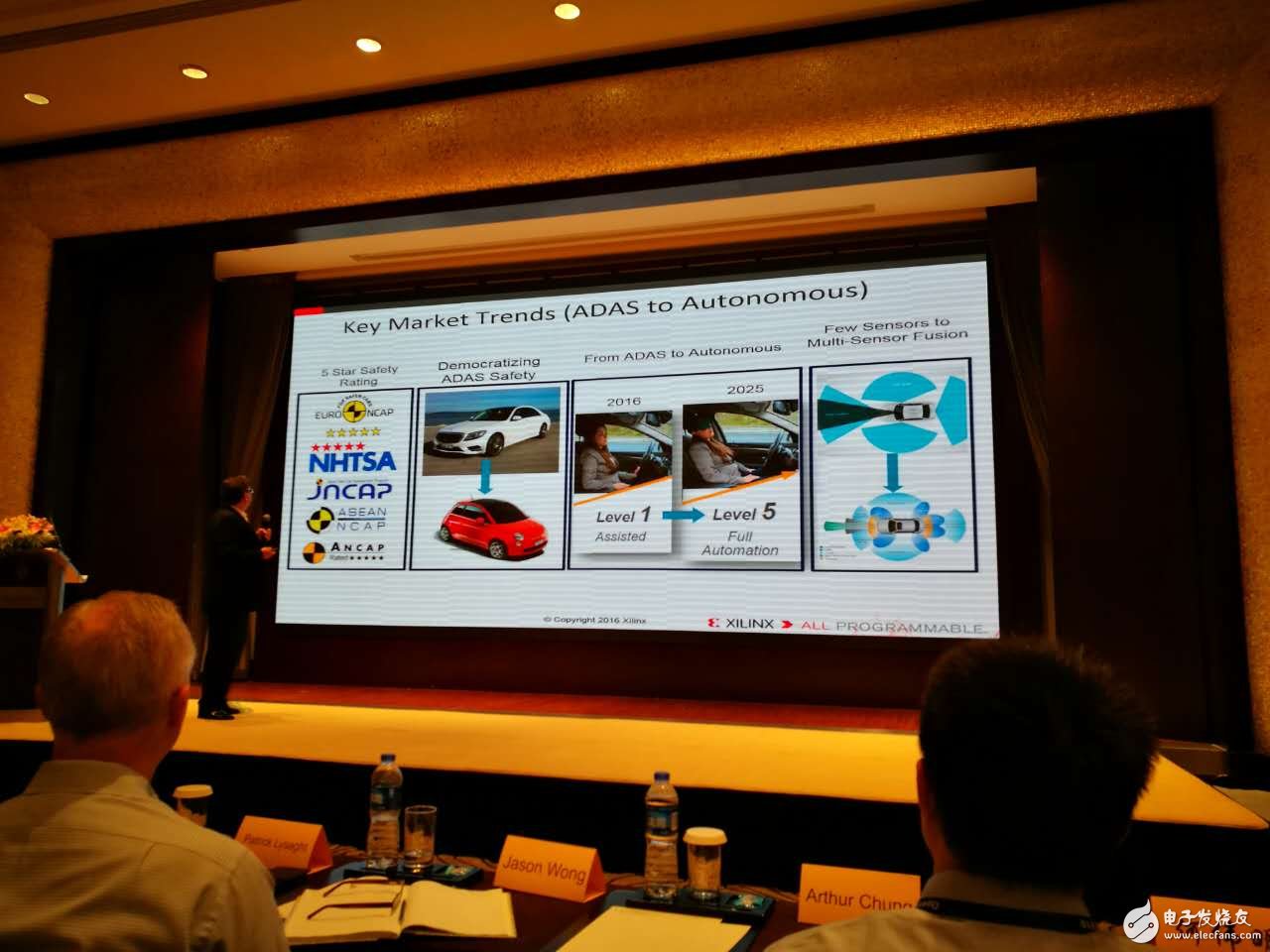

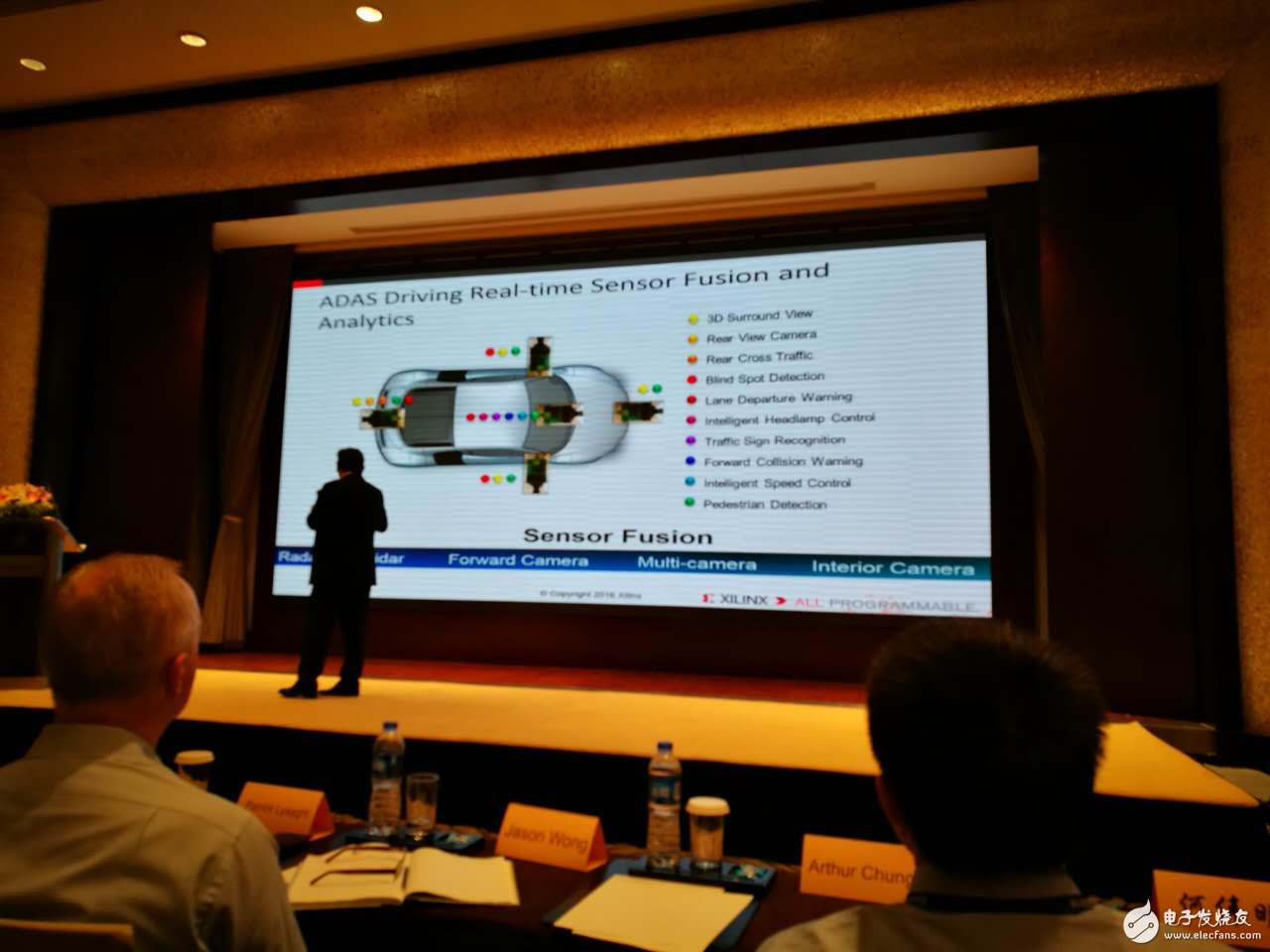

汽车ADAS方面:

神经网络处理:

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)