关键词:多采样率数字信号处理 软件无线电 数字上变频器 数字下变频器 数字抽取链 数字内插链

多采样率数字信号处理(MulTIrate Digital Signal Processing,MRDSP)是自20世纪70年代开始发展起来的数字信号处理领域的一门重要技术。1983年,R.E.Crochiere与L.R.Rabiner合写的专著《MulTIrate Digital Signal Processing》〔1〕的出版标志着该学科的基础理论已趋于成熟,但是,关于MRDSP的更深一层的应用至今仍在迅速地发展。所谓多采样率,就是指在一个系统中存在着两个或两个以上的采样率,其目的就是为了减少运算量和存储量,以便于信号的存储 、传送和处理。随着信号处理技术的发展,MRDSP已广泛应用于信号处理的各领域。如今,随着软件无线电〔3〕〔4〕的兴起,MRDSP已成为软件无线电的关键技术之一。

1 多采样率数字信号处理〔1〕〔2〕

1.1 多采样率数字信号处理的基本内容

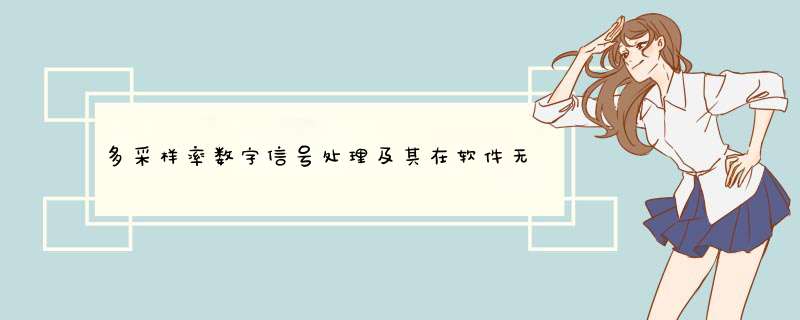

MRDSP的主要问题就是要设计一个有效的系统,使数字信号的采样率提高或者降低任意倍。我们把降低信号采样率的过程叫做抽取,亦称采样率压缩,而把提高信号采样率的过程叫做内插,亦称采样率扩张。基本的采样率变换有整数D倍抽取、整数I倍内插和分数I/D倍的采样率变换,如图1所示。图1中,信号序列的不同下标表示不同的采样率,fs为信号的原始采样率。图中,“↓D”表示D倍抽取,即

每D个原始采样抽取一个;“↑I”表示I倍零值内插,即每两个相邻原始采样点之间均匀地插入I-1个零点。其中的滤波器是为了滤除抽取中的混叠信号频谱和内插中的镜像信号频谱,它们分别称为“抗混叠滤波器”和“去镜像滤波器”。

图1中,x(n1)、w(n1)、w(n2)、y(n2)、y(n3)表示的是数字信号序列(输入、输出或经过中间处理后的);h(n1)、h(n2)为数字滤波器(系数);其中的n1、n2、n3表示的是具有不同采样率的数字信号或数字滤波器,而各自对应的采样率即为箭头上面所示。

图1只是基本采样率变换的概念性框图,由于其中的滤波器运算均在系统采样率最高处进行,所以,从运算量角度来说它们是低效的。实际中,总是采用采样率变换的高效网络结构,它主要有高效的直接式结构和高效的多相式结构等,其共同点是通过各种网络的等效变换,将滤波器中的乘法运算安排在最低采样率下;这样,对于D倍抽取、I倍内插和I/D倍的采样率变换可使其每秒乘法次数分别降低D、I和DI倍。由于对线性相位特性及稳定性的要求和容易实现高效结构的原因,采样率变换系统中的滤波器通常都是FIR(Finite ImpulseResponse)滤波器。若FIR滤波器是对称的,则在高效的直接式结构中可使乘法率再降低约一倍。为了进一步降低系统的运算量和存储量,针对采样率变换率为I/D的下述三种情形,我们经常用多级实现来代替单级实现:(1)D>>1,I=1;(2)I>>1,D=1;(3)D>>1,I>>1,I/D≈1。多级实现除了可以降低运算量和存储量外,它还可以简化滤波器的设计、减小滤波器系数的有限字长效应的影响等,但其代价是需要增加额外的控制结构。

1.2 两类高效的数字滤波器

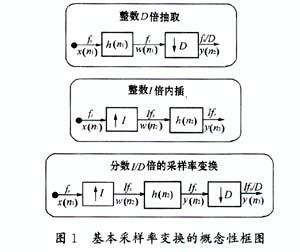

在实际的可编程硬件采样率变换系统中,用得更多的FIR滤波器则是两类高效的数字滤波器:半带滤波器(Half-Band Filter,HBF)和级联积分梳状滤波器(Cascaded Integrator-Comb Filter,CICF)。由于各自滤波器系数的特殊性,它们在节省运算量和存储量方面显得特别有效 。设某一HBF的阶数为N,则

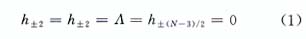

即除h0以外的所有偶序号的滤波器系数均为0。所以,应用HBF可以使系统的运算量和存储量同时再降低约一半。由于其频响特性的特殊性,HBF只能用于变换因子为2的抽取或内插过程。CICF〔5〕则更简单,所有的滤波器系数均为1,因而CICF又称为简单整系数滤波器。在滤波器的实现时,CICF将只有加法而没有乘法,更无需专门的存储器用于存储滤波器的系数。滤波器的结构也相当规整,我们可以容易地写出一个N阶CICF的系统函数

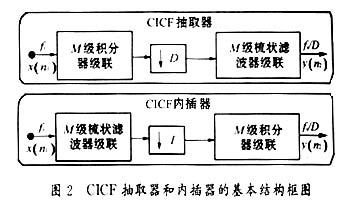

可见,一个CICF可以看作由一个积分器与一个梳状滤波器的级联,这就是CICF名字的由来。根据式(2)我们可以算出CICF的第一旁瓣峰值相对于主瓣峰值仅衰减约13.46dB。为了加大阻带衰减 ,我们通常将几级CICF级联起来。图2为M级CICF级联的D倍抽取器和I倍内插器的结构框图。由于在多级实现的抽取系统的首级和内插系统的末级,信号的归一化带宽较小,阻带特性容易满足 ,而且在这些变换级中信号的采样率过高,使得乘法运算极不经济,首要任务就是把信号的采样率降下来。因此,CICF经常用于抽取系统的首级或内插系统的末级。

2 多采样率数字信号处理在软件无线电中的硬件实现

2.1 软件无线电中的多采样率数字信号处理

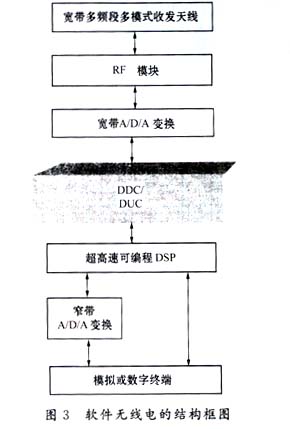

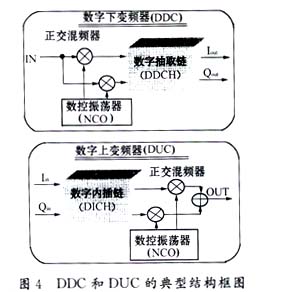

软件无线电正代表着包括无线通信在内的几乎所有的无线电电子信息系统的发展总趋势,其核心思想就是将A/D/A(模数/数模变换)变换器尽量靠近天线,在对信号充分数字化的基础上依靠软件来定义无线电的各项功能。理想的软件无线电应是对射频信号直接进行数字化,即数字射频软件无线电;而在现阶段则由于各种关键器件,特别是ADC(模数变换器)和DSP(数字信号处理器)发展水平的限制,数字中频软件无线电正成为理想软件无线电的一种经济、适用的折中选择。无论是数字射频还是数字中频软件无线电,数字下变频器(Digital Downconverter,DDC)和数字上变频器(Digital Upconverter,DUC)通常都是必不可少的关键器件,如图3所示。其原因有二:一是为了降低输入DSP的信号的采样率,以减轻DSP的运算负荷;二是通常信号的带宽仅为几百kHz以下,没有必要采用过高的采样率,这就使得采样率的降低成为可能。DDC和DDC主要有三大功能:变频(上变频或下变频)、采样率变换(压缩或扩张)和低通滤波。其中的采样率变换和低通滤波在实际系统中是以多级级联的形式由同一个功能模块来完成的,这里我们将该模块在DDC和DDC中分别称为数字抽取链(Digital DecimaTIon Chain,DDCH)和数字内插链(Digital InterpolaTIon Chain,DICH)。DDCH和DICH在本质上说就是采样率变换的多级实现,因此其理论基础是MRDSP。图4为DDC和DDC的典型结构框图。由图可见,DDC和DUC在结构上具有互易性。在下面的讨论中我们将会发现,其中的DDCH和DICH也有同样的关系。

软件无线电中的硬件数字抽取链和数字内插链应当具有方便的通用可编程性,我们可以根据自己的需要用FPGA或ASIC等进行专门设计,但更为经济、快捷的途径则是采用现成的商用数字下变频器和数字上变频器器件。商用DDC和DUC把变频和DDCH或DICH甚至是部分的解调或调制等功能模块都集成在同一块芯片上,节省了许多的设计开发时间和成本。尽管不同厂商的DDC和DUC千差万别,但它们的基本结构都是一样的(如图4所示),其最核心的功能模块就是DDCH和DICH。这里,我们挑选了目前单通道DDC和DUC中两种结构典型、性能先进并倍受青睐的商用器件进行讨论:一是Intersil公司(即99年8月份更名前的Harris公司)的SP50214B可编程下变频器(PDC),二是Analog Devices公司的AD9856正交上变频器(QDUC)。由于讨论的是MRDSP的硬件实现,所以我们仅研究这两种器件中的DDCH和DICH。

2.2 DDCH与DICH的两种典型的硬件实现

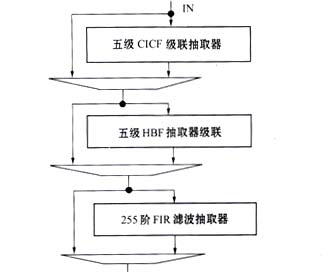

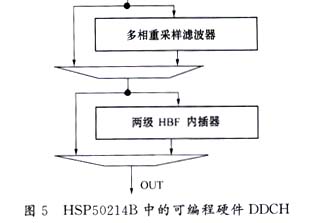

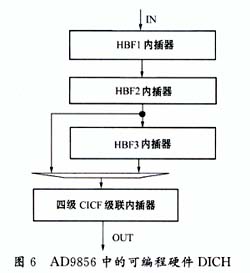

DDC中的DDCH和DUC中的DICH均有完全相同的正交两路,这是为了数字信号处理的方便和信号采样率的进一步降低;我们这里仅选其中的任意一路进行研究。图5为HSP50214B中可编程DDCH的具体硬件实现结构,图6为AD9856中的可编程DICH的具体硬件实现结构。

如前所述,由于半带滤波器(HBF)与级联积分梳状滤波器(CICF)在节省运算量和存储量方面均具有独到的优势,所以几乎所有商品化的DDC和DUC产品均采用了这两类滤波器,HSP50214和AD9856也不例外。正如我们所预料的,CICF均以级联的形式被分别安排在数字抽取链的首级和数字内插链的末级,用以承担较大的抽取因子和内插因子;并且,CICF滤波器结构规则,无需另外设计,比较容易修改抽取因子,可编程性能好。其中,上述数字抽取链中的CICF为5级级联,可承受的抽取因子为4~32之间的整数;数字内插链中的CICF为4级级联,可承受的内插因子为2~63之间的整数。HBF则在实现采样率变化因子为2时特别有效。虽然采用HBF的抽取器的抽取因子较小且不可变,但我们可以通过若干级HBF抽取器级联,通过选取不同的级数以达到改变HBF级抽取因子的目的。这里的数字抽取链采用了5级HBF抽取器级联的形式,而数字内插链则采用了3级HBF级联的形式。考虑到数字下变频器还必须较好地完成对信号的滤波整形功能,而HBF与CICF在这方面又存在缺陷,所以,面向滤波整形功能的普通FIR滤波器在数字抽取链中通常又是必不可少的。滤波整形FIR级在数字抽取链中一般都是位于CICF和HBF级之后,以便在较低的采样率下更加有效地实现,而且在CICF和HBF完成主要的采样率变化功能的情况下,该级通常不承担或只完成较小的抽取因子;所有这些都是为了使得可编程FIR抽取滤波器具有更高的可用阶数,更有效地完成滤波整形功能。AD9856之所以没有采用可编程FIR级是出于假设进入数字上变频器的基带信号已经能够满足信号频谱的技术要求。由于无法预知接收信号所处的频段和所需的确切采样率,所以作为接收用的数字下变频器还必须考虑到实际中常有的采样率变换非整数倍的情况。为此,HSP50214B中的数字抽取链还包含了面向采样率变换为分数倍的“重采样”级,由于该级的内插部分采用了多相结构,所以在此称为“多相重采样滤波器”。而作为发射用的数字上变频器通常是不需要重采样级的。为了恢复前面由于抽取而损失的时间分辨率和进一步降低可编程FIR级的采样率,以更充分地利用滤波整形功能,HSP50214B还在整个DDCH的最后部分增加了两级HBF内插级,这是HSP50214B在设计方面的独到之处。另外,比较图5和图6我们可以看出,HSP50214B中数字抽取链的每一级都可以被使能或旁路,这就更增加了其可编程性;而AD9856则只有HBF3内插器可以被使能或旁路。

本文介绍的DDCH和DICH都同时具有先进性和典型性,我们希望这些内容对软件无线电设计者和使用者能有所启发。

参考文献

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)