ADC的数字I/O线路也是噪声入口。数字I/O具有多种不同功能,因此噪声进入ADC的方式也不同。最明显的是数字输出接口。在此更值得关注的是采用CMOS输出的ADC,因为其采用单端输出。

通常,采用LVDS输出或串行JESD204B接口的ADC抗噪声耦合能力更强。除了数字输出,ADC本身的数字电路越来越多,为噪声通过控制线路进入提供了一些潜在的入口点。由于数字内容增加,不得不为这些功能提供I/O。有时,通过SPI(串行端口接口)完成附加I/O。而有时,SPI不能处理所有需求。

关于SPI的补充:SPI不仅是一个潜在的噪声入口,也可能造成其他转换问题。很多人建议,当系统运行时(当转换正在发生时)不要访问ADC的SPI。

其他I/O包括模式控制、关断、待机、超范围指示器、同步引脚等。所有这些都需要重视,为了避免噪声耦合,除了好的布局,还要确保正确的去耦合。

也许最容易忽视的入口就是ADC的接地。请注意,当说到“接地”的时候,指的是“电路公共端”。同时请注意,接地连接通常会有多个,例如模拟地和数字地。对于这两种接地,有时需要考虑它们在哪儿结合或连接在一起。

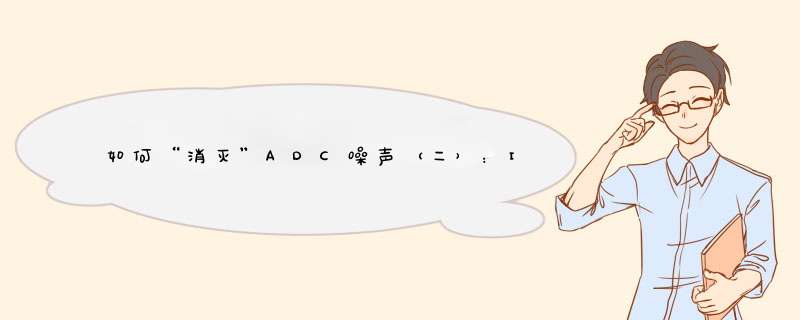

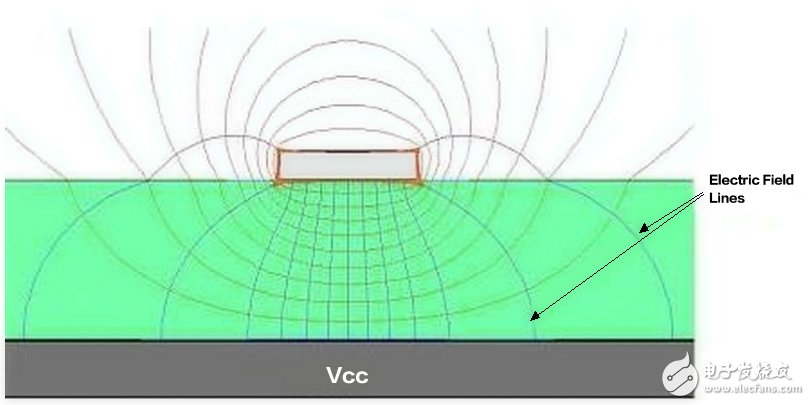

接地通常很自然地被认为是可靠的基准点。然而,接地并不总是稳定的基准点,也可能允许噪声进入ADC。重视系统设计和布局中的接地层是相当重要的,以便确保有足够的平面面积无割裂、接地过孔充足,以形成正确的电流返回路径。必须考虑设计中的所有电流返回路径,而不是假定接地是稳定的基准点。

系统设计如不当,噪声可能出现在接地层并可以进入ADC。通过参考阅读Bill Schweber的文章“了解你的接地”和Bruce Archambeault的文章“接地的秘密”,可以更深入地了解接地、接地电流、接地阻抗和电磁场。Bruce专门讨论了走线中的电流与处于走线正下方层中的接地或电源层是如何相互影响的,以及造成的问题。

在意料外的位置流动的电流,严格意义上来说不是噪声,但显然是麻烦。

现在已具备所有信息,可以正确考虑噪声进入ADC的入口。在此过程中,正确了解噪声进入ADC的不同方式,以及对抗噪声的方法,能够有效帮助广大工程师完成优秀的系统设计。

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)