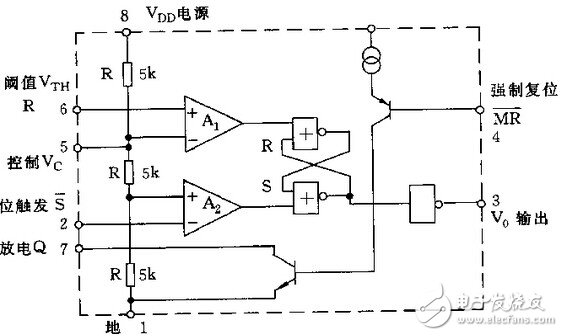

555定时器是一种模拟和数字功能相结合的中规模集成器件。一般用双极型(TTL)工艺制作的称为555,用互补金属氧化物(CMOS)工艺制作的称为7555,除单定时器外,还有对应的双定时器556/7556。555定时器的电源电压范围宽,可在4.5V~16V工作,7555可在3~18V工作,输出驱动电流约为200mA,因而其输出可与TTL、CMOS或者模拟电路电平兼容。1972年,美国SigneTIcs公司研制555定时器用于取代机械式定时器的中规模集成电路,因输入端设计有三个5kΩ的电阻而得名。

一、基本原理

555时基电路的工作过程如下:当2脚,即比较器A2的反相输入端加进电位低于?VDD的触发信号时,则VT9、VTll导通,给双稳态触发器中的VTl4提供一偏流,使VTl4饱和导通,它的饱和压降Vces箝制VTl5的基极处于低电平,使VTl5截止,VTl7饱和,从而使VTl8截止,VTl9导通,VT20完全饱和导通,VT21截止。因此,输出端3脚输出高电平。此时,不管6端(阈值电压)为何种电平,由于双稳态触发器(VTl4-VTl7)中的4.7kΩ电阻的正反馈作用(VTl5的基极电流是通过该电阻提供的),3脚输出高电平状态一直保持到6脚出现高于?VDD的电平为止。当触发信号消失后,即比较器A2反相输入端2脚的电位高于?VDD,则VT9、VTll截止,VTl4因无偏流而截止,此时若6脚无触发输入,则VTl7的Vces饱和压降通过4.7kΩ电阻维持VTl3截止,使VTl7饱和稳态不变,故输出端3脚仍维持高电平。同时,VTl8的截止使VT6也截止。当触发信号加到6脚时,且电位高于?VDD时,则VTl、VT2、VT3皆导通。此时,若2脚无外加触发信号使VT9、VTl4截止,则VT3的集电极电流供给VTl5偏流,使该级饱和导通,导致VTl7截止,进而VTl8导通,VTl9、VT2。都截止,VT21饱和导通,故3脚输出低电平。当6脚的触发信号消失后,即该脚电位降至低于?VDD时,则VTl、VT2、VT3皆截止,使VTl5得不到偏流。此时,若2脚仍无触发信号,则VTl5通过4.7kΩ电阻得到偏流,使VTl5维持饱和导通,VTl7截止的稳态,使3脚输出端维持在低电平状态。同时,VTl8的导通,使放电级VT6饱和导通。通过上面两种状态的分析,可以发现:只要2脚的电位低于?VDD,即有触发信号加入时,必使输出端3脚为高电平;而当6脚的电位高于?VDD时,即有触发信号加进时,且同时2脚的电位高于?VDD时,才能使输出端3脚有低电平输出。4脚为复位端。当在该脚加有触发信号,即其电位低于导通的饱和压降0.3V时,VT8导通,其发射极电位低于lV,因有D3接入,VTl7为截止状态,VTl8、VT21饱和导通,输出端3脚为低电平。此时,不管2脚、6脚为何电位,均不能改变这种状态。因VT8的发射极通过D3及VTl7的发射极到地,故VT8的发射极电位任何情况下不会比1.4V电压高。因此,当复位端4脚电位高于1.4V时,VT8处于反偏状态而不起作用,也就是说,此时输出端3脚的电平只取决于2脚、6脚的电位。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)