多路同步数字调相信号源一般采用单片机和多片专用DDS芯片配合实现。该技术同步实现复杂,成本高。给出了一种基于FPGA的多路同步信号源的设计方法,通过VHDL语言硬件编程实现了基于单片FPGA的多路同步信号,数字调相快速准确。利用QuartusⅡ进行综合和仿真验证了该设计的正确性,该设计具有调相方便、速度快、成本低等优点。

引 言

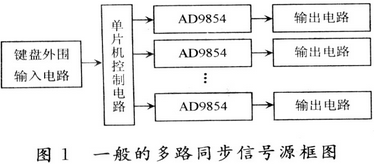

实现信号源的多路同步输出,在雷达、通信等多领域有着重要的应用。为了实现此功能,大多数设计是利用多个专用DDS芯片外围借助单片机帮助,实现多信号同步输出,如图1所示。

系统工作时,根据键盘输入,单片机输出频率控制字和相位控制字以及波形选择字,控制专用DDS芯片AD9854产生特定频率和相位的波形,经滤波放大后输出要求的模拟波形。为输出频率相同,相位相关的多路同步信号,控制数据由键盘输入,单片机向各专用DDS芯片输出相同的频率控制字和不同的相位控制字指令,控制各专用DDS芯片输出指定的频率和相位的波形。这样就从整体上实现了频率和相位的连续可调及同步。

AD9854是美国AD公司的DDS系列产品,性能良好,频率可调范围宽。在这样的设计中,利用AD公司的AD9854芯片,尽管有频率可调范围宽,波形丰富,实现调副、调频容易等特点,但是由于是采用分立的专用DDS芯片,各芯片参数很难做到完全相同,参数的差异会造成输出信号频率和相位不同。因此,尽管各DDS芯片采用同一频率字,各个输出信号频率也难以完全相同。同样,由于参数的不一致,波形之间的相位也难以准确调整到位,更重要的是各个信号频率差异的累积效应可能会导致同步失败。另外,专用DDS芯片价格昂贵,设计成本也较高。

基于以上原因,这里给出一种基于单片FPGA的多路同步信号源的设计方案,这种方案具有实现简单、同步性好等优点,且成本较低。

1 基于FPGA技术的多路同步信号源的设计模型

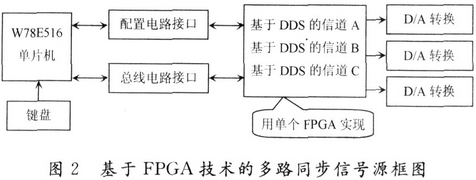

基于FPGA技术的多路同步信号源的整体框图如图2所示。

在本框图中,以三路输出为例,在一个FPGA芯片中,实现了三路基于DDs的信号通道,完成传统上三个专用DDS芯片AD9854完成的功能,实现三路波形的数字输出,在数字信号输出后进行D/A转换,实现三路信号的模拟输出。三个DDS信道频率取自同一个累加器输出的地址值,进行查表,同时相位的加法实现也是针对同一个累加器输出的地址,消除了分立专用DDS芯片计算的误差。由于在一块芯片中实现,所以各DDS信道的参数一致性好,分立专用DDS芯片的外部连线带来的延时误差也被降到最低。因此,通过以上措施,可以大大改善信号的一致性,可实现精准的相位连续调节。

单片机及总线配置电路通过键盘实现人机接口。通过4×4矩阵式键盘可以将频率选择、初始相位选择等数据输入单片机并经单片机处理后送FPGA,实现DDS的调整。

FPGA是完成DDS多信号产生的核心部件,完成DDS多路同步信号的产生。

2 基于DDS技术的多路同步信号输出的FPGA核心设计

2.1 一般DDS的工作原理

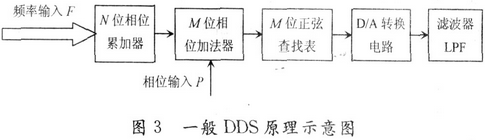

DDS(Direct Digital Synthesizer)是从相位概念出发直接合成所需的波形的一种频率合成技术。一个DDS信号发生器是由:相位累加器、波形数ROM表、D/A转换器以及模拟低通滤波器LPF组成,原理框图如图3所示。DDS技术的核心是相位累加器,相位累加器在稳定时钟信号的控制下产生读取数据的地址值,随后通过查表变换,地址值被转化为信号波形的数字幅度序列,再由数/模变换器(D/A)将代表波形幅度的数字序列转化为模拟电压,最后经由低通滤波器将D/A输出的阶梯状波形平滑为所需的连续波形。相位累加器在时钟Fc的控制下以步长F作累加,输出的值与相位控制字P相加后形成查表的地址值,对波形ROM进行寻址。波形ROM的输出值即是幅度值,经过D/A变换后形成阶梯状的波形,最后通过低通滤波平滑成所需的波形。合成信号的波形取决于ROM表中的幅度序列,通过修改数据可以产生任意波形,如果要产生多种波形,只需把所需的多种波形数据存放到波形ROM表中。一般DDS的原理示意图如图3所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)