在设计可编程门阵列(FPGA)电路时,必须极端重视电源问题,从而使最终产品能在所有可能的条件下无缺陷工作并处于最优状态。FPGA 电路电源有两项需考虑的问题: FPGA 电路上电要求和电路功耗分析。这篇文章针对这两方面的要求,讨论您可能遇到的问题,以及解决方案。

目前FPGA电路设计所面临的问题

FPGA电路通常需要多路电源输入。为优化开机时的电流拖曳,防止锁死和永久性的电路损坏,同时也为了防止开机接通时的毛刺干扰和降低开机接通的功耗,这些电源输入必须具有精确的上电序列以及正确的电压变化率。如何实现复杂多路供电的精确控制是FPGA电路设计验证过程中的难点。此外,随着项目的发展,FPGA电路设计指标通常会发生变化,灵活简单的上电参数调整方式也是工程师在进行前期电路设计时所需要的。

在产品设计过程中,还需要测试各种工作条件下的FPGA电路功耗,捕获大电流尖峰的精确轮廓,并带有时戳,以确定尖峰出现的时间,从而确定设计必须提供的最大电源功耗。可能还需要为电源资源有限的产品(如电池供电设备)进行进一步功耗优化设计。

实例: 为 Xilinx Spartan-3 FPGA 设置上电规则并进行功耗分析

为验证不同上电时序对FPGA电路消耗电流的影响,使用安捷伦 N6705A直流功耗分析仪按图1所示与FPGA电路进行连接。

图1 使用多路电源为FPGA电路供电时的连接和设置

首先按照 图2 所示,为FPGA电路设置上电时序,VINTF 最早打开输出,VCCINT 在VCCO 之前1毫秒打开供电:

图2 N6705A上电序列设置屏

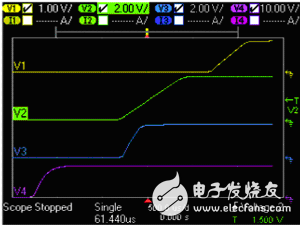

在此供电情况下,可以看到内核电源消耗的电流 ICCINT 在上电过程中产生一个明显的脉冲尖峰,如图3 所示:

图3 内核电源VCCINT在上电过程中所消耗的电流波形ICCINT

按图4 所示重新改变上电时序,使VCCINT上电输出滞后于VCCAUX 1毫秒,此时可以看到ICCINT 电流波形中脉冲尖峰已经消失。

图4 调整上电时序后,ICCINT 的电流波形

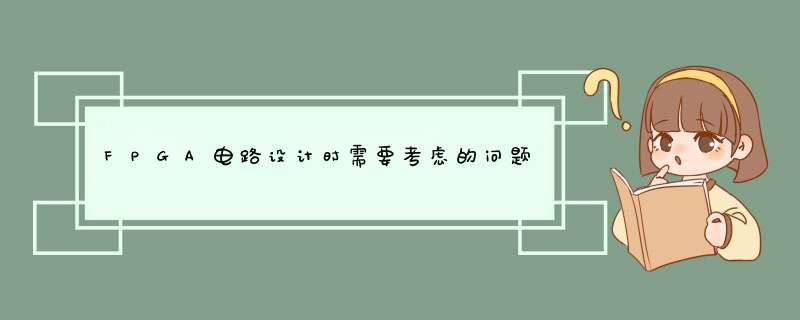

同样,为实现VCCINT 和VCCO 的上电斜率要求,并验证在规定的上电斜率范围内FPGA电路的工作情况,可以使用N6705A按照 图5 所示分别设置各路供电的上电斜率。

图5 供电电路电压斜率的设置

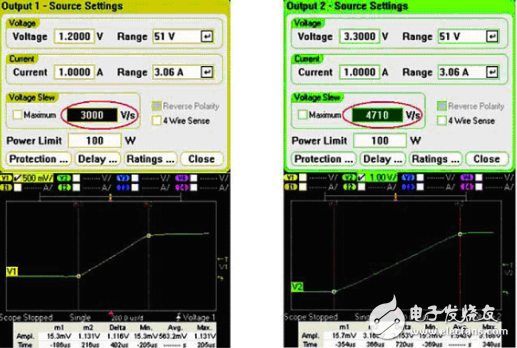

为保证成功上电,FPGA电路的电源电压必须通过各自的电压阈值范围,并且不能有电压跌落。图6 显示电源接通时具有正确上电序列和上升斜率的各路供电输出。每一路电压都平稳上升,并且没有跌落和其它不稳定行为。这说明在当前的供电条件下,FPGA电路可以正常工作。

图6 按照设定的上电序列和斜率进行供电的电压波形

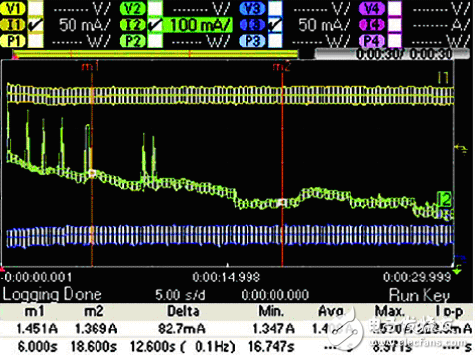

对FPGA电路的连续功耗分析,可以通过高速采集各路供电的电流值来完成。连续高速采集可以保证捕捉到的所有的电流脉冲细节,但数据量也会急剧增大。为保证采集速度同时减小数据量,可以通过设定采样周期的办法,在每个周期内,对高速采样到的电流结果计算平均值和最大/最小值。整个过程必须保证连续采集,不会有电流数据丢失。同时还需要保留每个数据点所对应的时间信息,以便事后对大电流脉冲产生原因进行分析。这里同样可以使用N6705A对多达四路供电进行长时间数据采集。其采样结果如 图7 所示:

图7 N6705A对ICCINT、ICCAUX和ICCO电流连续采集30秒的结果

结论

在应对FPGA电路电源设计部分的相关问题时,供电验证和耗电分析往往是工程师所面临的最大挑战。设计师需要在FPGA允许范围内通过精调上电序列和变化斜率优化开机功耗,并验证消耗电流的变化。为能够快速精确调整供电设置,并实时测量消耗电流值,使用带有多路供电测量功能的高性能电源是最理想的选择。安捷伦N6705A直流功耗分析仪可以帮助工程师解决FPGA电路设计验证过程中所遇到的供电相关问题,帮助节省时间,人力和资金成本,快速达到设计目的。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)