Line Buffer

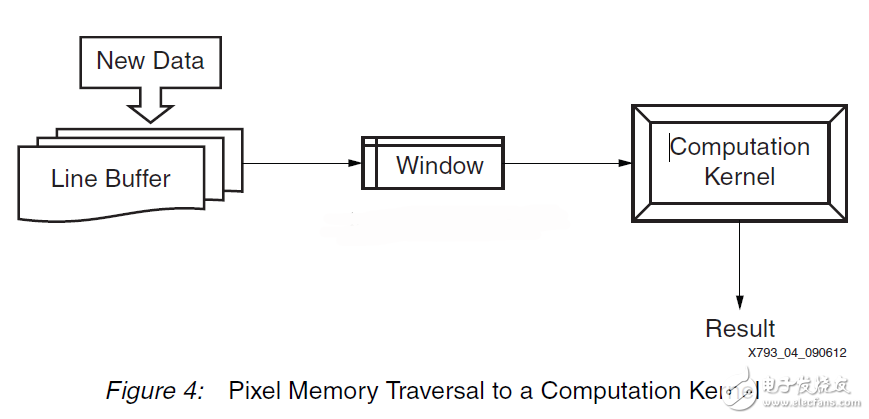

行缓冲区是一个多维移位寄存器,能够存储若干行的像素数据。通常情况下,线的缓冲块RAM实现避免通信延迟对片外存储器的记忆。此外,行缓冲区需要同时读和写访问,这需要充分利用的双端口的性质的块。虽然内存窗口是行缓冲区的一个子集,但是在大多数的视频和图像处理算法中,不能直接使用行缓冲区。图4中所示的是一个输入像素的路径遍历算法计算内核。

正如在窗口的情况下,一个行缓冲区被声明为一个多维数组。在确定行缓冲区的高度时,一个简单的规则是将其保持在同一高度的内存窗口中。例如,相应的行缓冲区窗口B在FPGA中声明为:

rgb_pixel D[3][MAX_COLS]

声明一个满三行的缓冲存储器在FPGA资源利用中效率是不高的,但在C / C + +里它是最简单的代码。该区域低效率是窗口处理算法的结果不需要一个完整的N行数据开始计算。在一些数据块上存储全部的N行而不是N-1条线路和一些像素的结果。根据设备的使用情况,在本文档中所示的例子代码可以进一步优化,以减少块内存消耗。

随着一个类似的移位寄存器的数据移动说明书中,一个行缓冲器需要用户重新考虑处理循环的边界的算法中。该算法必须考虑到行缓冲的两种效果。第一个效果是填充行缓冲器具有足够的数据来计算第一输出值所需的时间。第二个效果是,该算法将不得不运行更多的迭代比可用输入样本以产生所有输出采样。

用行缓冲器D中的例子继续,则该算法的计算循环扩展,如下所示。

for(row = 0; row < MAX_ROW; row++)

{

for(col = 0; col < MAX_COL; col++)

{

....

}

}

to

For(row = 0; row < MAX_ROW+1; row++)

{

for(col = 0; col < MAX_COL+1; col++)

{

....

}

}

边界条件的由1占由一个行缓冲器的插入创建的输入和输出数据之间的偏移的扩展。与延伸超过输入数据集的边界的处理的循环中,用户必须添加选通条件,以确保该算法的正确功能。

在第一个代码示例中,该算法的输入范围是有界的。继的数据流的第二个例子,所有的输入数据是最初写的线缓冲区。这意味着,门条件必须放置在输入数据写入到该行缓冲器。输入数据选通条件的一个例子如下所示。

if(col < MAX_COL & row < MAX_ROW)

{

D[2][col] = new_data[k];

}

输出接口的写入结果也必须被延迟到该行缓冲区延迟。例如,一个条件的一个例子来显示输出。

if(col > 0 & row > 0)

{

output_pixel[k] = result;

}

在行缓冲区中的数据移动是一个垂直的移位,在新的行被添加为旧行被丢弃。该线沿柱轴自动发生的由于内部循环处理过的线上校垂直移位可编码如下图所示的水平移动。

if(col < MAX_COL)

{

D[0][col] = D[1][col];

D[1][col] = D[2][col];

}

转载自:Running的专栏

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)