运算放大器是模拟电路中最重要和最通用的单元电路之一,同时也是许多模拟系统和数/模混合信号系统中的一个完整模块。运放具有足够大的正向增益,当加负反馈时,闭环传输函数与运算放大器的增益几乎无关。利用这个原理可以设计很多有用的模拟电路和系统。对运算放大器最主要的要求是有一个足够大的开环增益以符合负反馈的概念。模拟电路的速度和精度与运算放大器的性能有关,为了得到更快的速度和更高的精度,要求运算放大器具有更宽的单位增益带宽和更高的直流电压增益。

目前常见的几种放大器结构包括两级运算放大器、套筒式共源共栅放大器以及折叠共源共栅运放等。两级运放的输出摆幅在各种放大器结构中是最大的,然而其主要缺点是频率特性差;套筒式运放在各种放大器结构中功耗最低、频率特性好、速度高和带宽大,但该电路的信号共模输入范围和输出摆幅太小;折叠式共源共栅运算放大器具有增益带宽大、低频增益高、摆幅大、速度高、频率特性好等诸多优点,得到广泛应用。R Assaad等人提出的复用型折叠式共源共栅(Recycling Folded Cascode,RFC)结构比折叠共源共栅运算放大器具有更高的增益带宽、低频增益和摆率,同时并不增加功耗和设计面积。本文利用复用型折叠式共源共栅单级运放结构,在5 V电压下驱动5 pF负载电容,设计了一个单级运放。使增益带宽为52.79 MHz,低频开环增益为71.7 dB,相位裕度为60.45°,相比文献中的折叠式共源共栅运算放大器的增益带宽4.05 MHz,提高了约13倍;低频开环增益为43.5 dB,提高了28 dB;相位裕度为59°,而相位裕度在60°以上系统趋于稳定,所以该复用型折叠式共源共栅单级运放结构系统稳定性上也有一定改善。

1 电路分析以及设计

1.1 折叠式共源共栅运算放大器电路分析

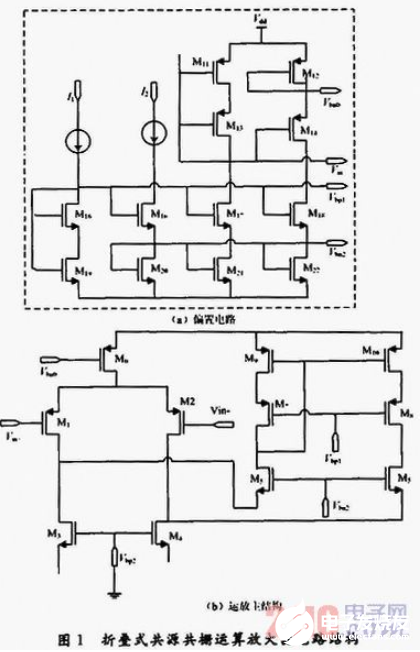

文献中的折叠式共源共栅运算放大器的输入级均采用差分放大器的电路结构,选用输入管时,一般采用PMOS管,整个电路的结构如图1所示。

图1(a)为偏置电路,I1和I2是基准电流,偏置电路提供主电路中所用的所有偏置电压,在实际中为了满足匹配,偏置电路中管子长度应该与运放中相应的管子的长度相等。图1(b)为运放主结构,其中M0为折叠共源共栅运放的输入管提供偏置电流。M1,M2为PMOS差分输入管,M5,M6与M1,M2形成输入共源共栅管,M7,M8,M9,M10构成的共源共栅镜把双端输出转化成单端输出,并提高了输出阻抗,有益于提高增益。

1.2 RFC电路设计及分析

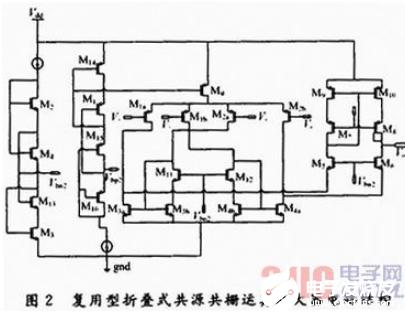

新型的复用型折叠式共源共栅运算放大器是从文献中折叠式共源共栅运算放大器的基础上改进而来。如图2的复用型折叠式共源共栅运算放大器主电路中,文献中折叠式共源共栅运算放大器的M1,M2被分成M1a,M1b,M2a,M2b,流过每个管子的电流为IO/2。M3,M4被分成电流镜M3a,M3b和M4a,M4b,比率为3:1,这种电流镜的跨接确保了小信号电流来源于M5,M6的源端,M11,M12的输入电压大小与M5,M6相同,设计管子宽长比尺寸一样,M11,M12维持了M3a,M3b,M4a,M4b漏电势,帮助改善它们之间的匹配性。

图2中左边部分为偏置电路,其中Vbp1为M0管提供偏置电流,Vbp2为M7,M8提供偏置电压。Vbn2为M5,M6,M11,M12提供偏置电压。I1,I2为外部引入的基准电流。在引入I2后,流过M1,M14,M15,M16的电流相同,根据电流公式,宽长比与Von(过驱动电压)成反比,调节宽长比使|Von|在120~400 mV之间,很容易就能得到Vbp1。计算Vbp1,Vbp2的方法相同。在电路进行DC仿真时,M1和M13工作在线性区。

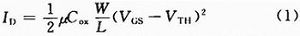

为了证明复用型折叠式共源共栅运算放大器相比文献中折叠式共源共栅运算放大器具有的优越性,在分析电路时,假定所有管子工作在饱和区,饱和区电流公式为:

首先分析两种电路的低频增益,低频增益的公式为:Av=GmR0。在折叠式共源共栅运算放大器运放中:GMFC=gm1;复用型折叠式共源共栅运算放大器中:GMRFC=4gm1a,考虑到M1的尺寸是M1a的2倍,由公式Gm=2I/(VGS-VTH)可知,gm1=2gm1a,在相同的输出电阻情况下,2倍的输入跨导,大约会给运放带来6 dB的增益提升。在两个运放的输出电阻分析中,由运放主电路的右边电路的小信号模型有:

ROFC=gm6 rds6(rds2‖rds4)‖gm8 rds8 rds10 (2)

RORFC=gm6 rds6(rds2a‖rds4a)‖gm8 rds8 rds10 (3)

假设其他参数相同的条件下,由公式rds=1/(λID)可知,RORFC比RRFC大。因此,复用型比传统型折叠式共源共栅运放在低频增益上有8~10 dB的提升。

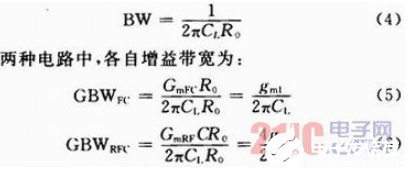

低频增益和带宽的乘积叫做增益带宽(GBW),目前它是放大器的品质因数,也是放大器的最重要的指标。在增益开始下降的那一点称为带宽BW或者-3 dB频率,它由输出电阻R与负载电容C的乘积所得的时间常数决定。在电路设计中,带宽公式为:

其中gm1=2gm1a,从公式可以看出GBWRFC比GBWFC要大很多。在设计复用型折叠式共源共栅运算放大器时,要使其稳定工作,其相位裕度(PM)要保证在60°以上。公式为:

式中:fp1为运放主极点;fp2运放非主极点;fz为运放零点。在复用型折叠式共源共栅运放中,主极点是由时间常数RORFC CL决定,非主极点由M5,M6源端寄生电容C2和该点的电阻R2的乘积决定。为了使运放的相位裕度保持在60°以上,必须使得非主极点频率大于2.2倍增益带宽。在复用型折叠式共源共栅中,M5,M4源端的寄生电容为:

C2=CGS5+CSB5+CGD3a+CdB3a+CGD1a+CdB1a

在图3中,M1a的电流I1a与M5的电流I5都流过M3a,M3a必须要有足够的栅宽以满足在比较小的驱动电压下能传导大电流,所以寄生电容CGD3a和CdB3a相当大。f2=1/(C2R2),C2大,f2就会变小。要使f2大于2.2倍增益带宽,必须推高f2。用减少流入M3a和M4a的电流的方法就可以达到目的。因为电流减小,M3a和M4a的栅宽也相应减小,从而C2也减小,f2便增大。

2 电路仿真结果

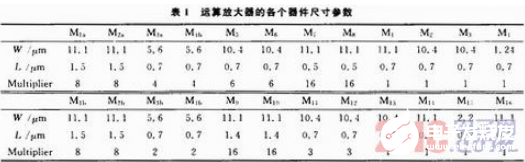

图2中各个MOS管的参数如表1所示。

所设计的电路仿真用Cadence公司的模拟仿真工具Spectre,仿真模型用CSMC0.5 μm标准CMOS工艺模型。电路交流仿真结果见图3。由图中增益曲线看出曲线在频率10 kHz处开始下降,所以带宽为10 kHz,增益为71.7 dB。频率大于10 kHz,其增益开始降低,降低到0 dB处的频率为增益带宽,值为52.79 MHz。由图中相位曲线看出,增益降为0 dB时,相位为-119.55°,相位裕度就为60.45°。所以电路增益带宽为52.79 MHz,低频增益为71.7 dB,相位裕度为60.45°。与文献中折叠式共源共栅运算放大器的增益带宽4.05 MHz,低频开环增益43.5 dB,相位裕度59°相比,其在增益,带宽和系统稳定性上都有很大提高。

3 结语

本文在文献中折叠共源共栅运放和复用型折叠共源共栅运放的分析基础上,设计了一种高性能折叠共源共栅单级运放,具有高开环低频增益、高增益带宽。采用CSMC0.5μm标准CMOS工艺模型,Cadence公司的模拟仿真工具Spectre对电路进行直流和交流仿真。结果表明:电路的增益带宽为52.79 MHz,低频开环增益为71.7 dB,相位裕度为60.45°,其各项指标与均有较大提高,设计令人满意。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)