引 言

作为机器人执行机构的伺服系统,其伺服性能和工作的可靠性对机器人的整体工作性能起着决定性的作用;但是传统的控制方法及其封闭式结构,已经不能满足现代伺服控制的要求。神经网络控制由于能够很好地克服机器人伺服系统中模型参数的变化和非线性等不确定因素的影响,很适合用于时变非线性、强耦合的工业机器人控制系统中。可编程片上系统SOPC和大规模现场可编程门阵列FPGA的出现,为神经网络控制器的硬件实现提供了新的载体。

本文以Altera FPGA及内含的一个Nios II嵌入式软核处理器作为上位机来研究机械手臂直流电机速度伺服控制器的片上可编程系统(SOPC)。根据模块化的设计思想,采用Verilog HDL语言,将神经网络控制器和其他电路模块在FPGA芯片内以硬件方式实现。

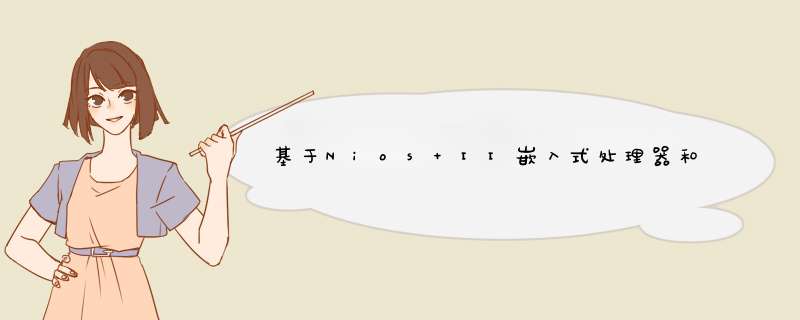

1、 系统总体结构

控制部分用A1trea公司C++yclone II EP2C35芯片取代了传统的单片机或DSP。FPGA与单片机最大的区别就在于它的并行性,能够并行地采集、处理和输出信号,是实现神经网络并行运算的关键,为提高整个系统的运行速度起了很大的作用。其FPGA芯片内集成的Nios II软核处理器作为上位机,根据末端执行器的速度,采用C++语言进行坐标变换和轨迹规划,定时向伺服控制系统发出控制命令和运行参数。系统总体框图如图1所示。

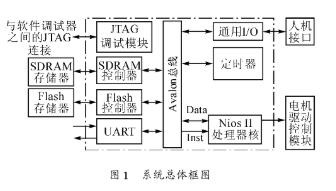

2 、电机运动控制模块的组成

伺服控制系统模块接收到速度给定信号和命令后进行速度调节,如图2所示。速度调节器的输出就是PWM脉宽调制电路的控制信号,之后产生PWM信号传给伺服电机驱动器驱动电机。速度反馈信号由装在电机轴上的光电编码器产生。为了提高反馈信号的分辨率,对光电编码器的输出信号进行倍频,从而提高了编码器的分辨率,也就提高了速度反馈信号的分辨率。速度调节采用神经网络参数辨识自适应控制。

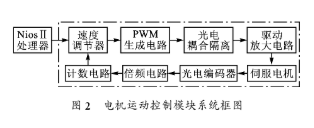

3、 参数辨识自适应控制系统

用作自适应控制器的BPNNC,输入为电机给定转速y与实际转速yf相比较得到的转速误差e及其变化率ec,输出为PWM的控制信号Vp(k)。用作参数辨识的BPN—NI的输入为驱动系统的实际输入(即BPNNC的输出值Vp)和电机实际转速yf,输出为辨识的系统输出y*。y*为预测转速,用y*代替yf,用作RBFNNC的在线训练。图3为参数辨识自适应控制框图。

2个BPNN都是两输入单输出网络,离线训练的样本均通过实验的方法获得。NNC的输入样本向量为Xci=(e(k),ec(k)},输出样本向量为Yci={Vp(k)}。NNI的输入样本向量XIi=(Vp(k一1),yf(k一1)},其输出样本向量为YIi={y*(k)}。网络参数的学习分为两步进行:先在离线训练中确定隐层节点的个数及其各层的网络连接初始权值,再通过在线训练自适应地调整权值。

4 、硬件电路的FPGA实现

4.1 BPNN在FPGA中的硬件可重构实现

目前基于SRAM工艺的FPGA具有易失性的特点,每次重新加电FPGA都要重配置,才能使FPGA进人工作状态。配置信息通常存放在片外存储器中,导致FPGA器件的资源配置可改变特性刚好可以满足由上述可知的BP网络的结构可重构、激活函数可重构和学习算法可重构的要求。

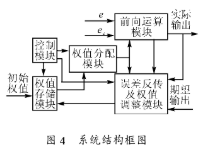

从计算的角度考虑,BP网络的算法可以划分成3个步骤,即前向传播、误差反向传播以及权值更新。但是考虑到神经网络的复杂性和设计文件的复用性,BP神经网络的硬件实现必须解决与算法有关的运算速度、计算精度、并行性和可存储性等问题。本着层次化、模块化的原则,采用由Verilog HDL硬件描述语言输入的自上而下的设计方法,把BP神经网络分为前向运算模块、误差反传及权值调整模块、权值存储模块、权值分配模块等几个大的功能模块。系统结构框图如图4所示。

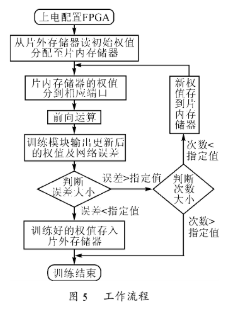

将各个BP网络运算模块进行组合就可以实现一整套人工神经网络,但是仅仅将这些模块简单连在一起并不能让网络进行工作或训练。还必须精确设定在每一个时钟沿对每一个模块发出正确的使能信号,使每一个模块处于工作状态或者停滞状态,并且还必须要有合适的地址信号发生器在正确的时间产生正确的地址信号,使每一次数据都能从正确的位置读出并写入正确的位置。本文根据BP算法的运算规则设计控制模块,并且采用一个共用的地址发生器,控制模块有7个输出信号,分别是前向模块使能信号、学习模块使能信号、片内RAM及地址产生模块使能信号、片内RAM写入控制信号wen、片内RAM读出控制信号ren、片外存储器写控制信号save、片外存储器读控制信号load。最后的控制器可以使网络进行离线训练时将前向模块、误差反传模块和相应的控制模块同时配置到FPGA中进行网络训练;而当训练好的网络正常工作时,只在FPGA中配置前向模块和相应的控制模块就可以高速运行该神经网络。工作流程如图5所示。

4.2 其他主要模块在FPGA中的实现

三角波脉宽调制器(PWM)采用等腰三角形作为载波,将输入信号与三角波信号比较产生。测速模块、鉴相倍频电路模块可根据其原理设置相应的乘法器和除法器即可实现。

5、 实验结果

参考文献通过对一些典型应用的研究和分析,认为16位定点数是不削弱神经网络能力的最小精度要求,并且为避免运算规模过于庞大和节约芯片资源,所以对32位的输出数据进行了截尾 *** 作,仅取32位中的前16位。

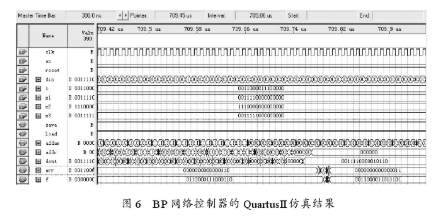

速度伺服控制器电路中的所有模块均用硬件语言Verilog HDL进行描述,在源代码通过功能仿真和时序仿真测试后,再综合生成网表文件,最后在Altera公司的Cyclone II EP2C35器件中实现,整个设计消耗的资源已经接近饱和。BP网络控制器的QuartusII仿真结果如图6所示。由图可知经过多次训练后系统输出值f接近于给定值t,误差err变小[llg2],小于给定误差。

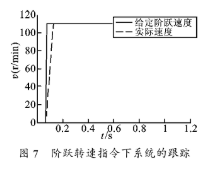

驱动对象是一台直流电机,输入电压是DC 27 V,额定电流为2.5 A,最大空载转速为600 r/min。图7为空载状态下转速指令由O上升到1lO r/min阶跃输入时的系统跟踪结果。由图7可知,系统能很快地响应给定转速的变化,有较好的跟踪能力和稳定性。

6、结 语

运用神经网络控制的方法,在FPGA中硬件实现速度反馈调控电路,采用C++语言在FPGA片内集成的NiosII软核处理器内进行坐标变换和轨迹规划,构成一个完整的机械臂关节速度控制器的SOPC系统。通过实验结果可知,此控制方案进一步提高了速度伺服系统的精度,增加了系统的集成度、抗干扰性和稳定性,同时提高了系统的调试效率,是现代机器人伺服系统向模块化、智能化发展的方向。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)