ps:高速设计的三座大山——电阻基础

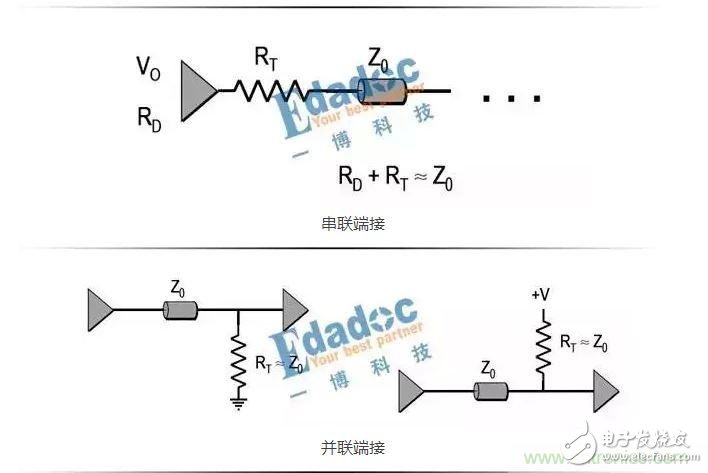

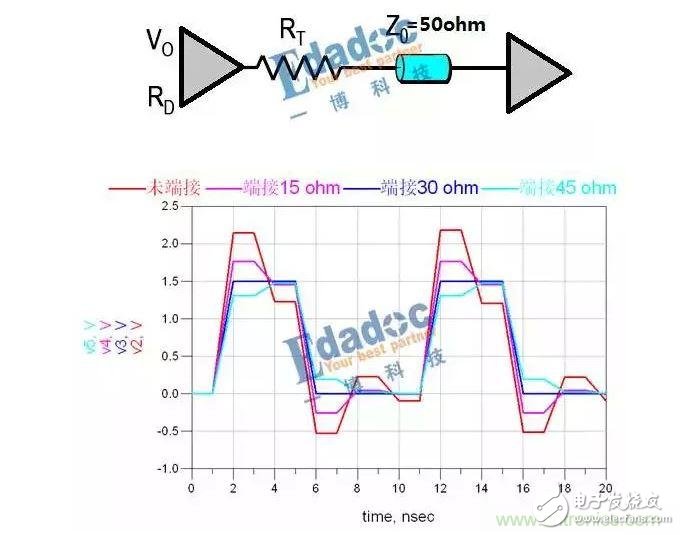

端接示意图如下:

各种端接都有其优缺点,以后有机会,高速先生会一一对以上各种端接做全面的分析,今天我要说的是:串联电阻对信号的影响,也就是串联端接所用的电阻对信号的影响。

先看图

串联端接电阻的大小会影响信号的上升沿,当串联电阻变大时,信号的上升沿变缓(另外信号幅值的变化是因为反射的原因,这个在反射详解系列,有详细解释,当端接30ohm时,匹配最好,没有反射)。

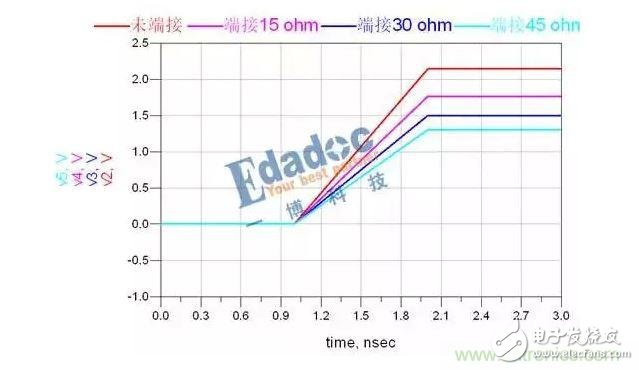

把图放大,上升沿看的更明显。

为什么信号的上升沿会变缓了呢?我们来梳理一下,整条链路有发送端、串阻、传输线、接收端,变化量是串阻的阻值,现象是上升沿变缓。有什么原理即跟R有关,又会导致上升沿变缓呢,最先想到的肯定就是RC滤波器。一阶RC滤波器是典型低通滤波器。串联电阻与传输线的等效电容、接收器的输入电容组成了RC滤波器,限制了信号的带宽。其影响信号带宽的原因是:R与C组成RC充电电路,电容两端的电压变化V_C=V_S×(1-e^(-1/τ t) ),其中τ=RC,是时间常数,当时间常数越大时,电容两端的电压变化越慢,信号边沿越缓。

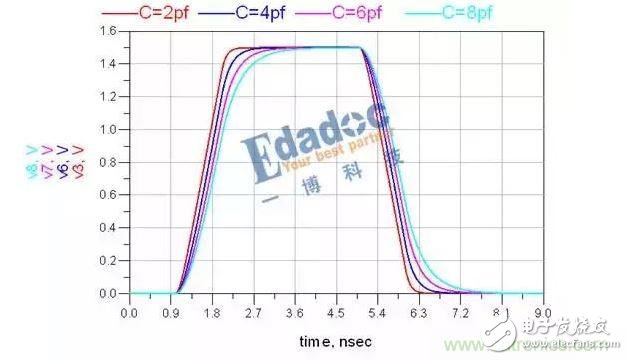

下面我们再来验证一下,固定串阻阻值不变,改变电容值,当电容阻值变大时,RC时间常数变大,上升沿同样变缓了。如下图:

以上就是串阻对信号影响的分析。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)