本文简要说明了当前IF/RF转换器中集成的典型DDC和DUC——它们是何物,为何需要它们,以及它们在信号链中如何工作。适当了解这些内容并正确使用它们将能减少资源占用并减轻FBGA/ASIC中的编码工作,以及节省系统的功耗和成本。

为了满足智能手机功能日益提高的数据需求,现代数字移动通信系统的基础设施必须持续发展以支持更宽的带宽和更快的数据转换。为实现高速的数据速率,数字转换器中的数字中频处理、包括DDC(数字下变频器)和DUC(数字上变频器)是其中主要的功能模块。

这些数字功能可在DSP和FPGA中实现,某些大公司也会构建自己的数字中频处理ASIC。ADI公司正在将越来越多的此类数字中频处理模块集成到高速转换器IC中,从而大幅减轻设计工作,节省系统成本和功耗。本文探讨ADI公司IF和RF转换器中的集成DDC和DUC通道,并说明它们在实际应用中如何工作。

高速转换器是现代无线基站系统的关健功能之一。越来越多的此类转换器集成了复杂的数字信号处理模块,以便简化系统设计中的FPGA工作。转换器中的数字信号处理模块对系统设计非常有益,但这些益处尚未得到很多工程师的全面了解。希望本文能给数据转换器中的DDC和DUC功能做一个清楚的说明,使系统设计人员能充分利用ADI转换器给收发器架构带来的好处。注意:本文将聚焦于ADC和DAC中的数字处理模块;因此,某些描述中将发射机和接收机模块加以合并。请忽略可能引起混淆的信号流向。

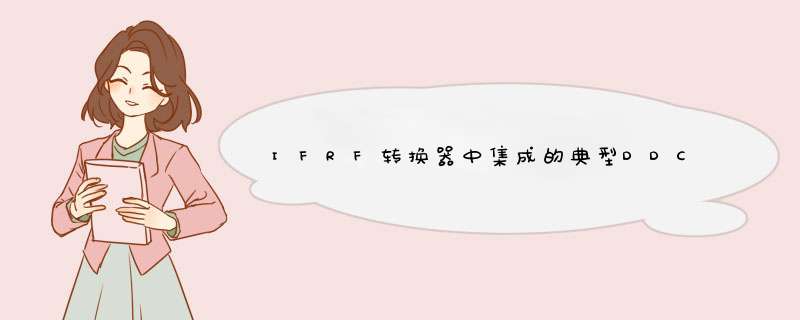

在现代数字移动通信系统中,发射和接收路径(包括下面描述中的反馈接收路径)可根据信号特性分为三个主要电路级:射频级、模拟中频级和数字中频级。图1是典型发射机和接收机的框图。射频级处理射频信号,在当前LTE标准中,其信号频率范围一般是700 MHz到3.8 GHz。

经过混频器、调制器或解调器—这些都是混频单元—处理后,射频信号移动到DC至300 MHz以下的较低频率。从数据转换器到混频器的处理模块包括转换器(ADC或DAC)、模拟滤波器和中频放大器。我们可以把该级称为模拟中频级。

转换器之后(事实上是在转换器的量化器部分之后),信号变为数字信号;它与随后的FPGA或ASIC一起,我们称之为数字中频级。对于此级中的各数字信号处理模块,在Tx路径中通常称之为DUC(数字上变频器),在Rx路径中通常称之为DDC(数字下变频器)。

直接射频架构是例外,其中数据转换器直接对射频信号采样,因而没有模拟中频级,信号链仅由射频级和数字中频级构成。

图1.发射机或接收机的典型框图。

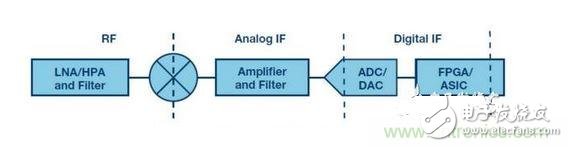

典型DDC模块包括载波选择、下变频器、滤波器和抽取器。这些功能模块按顺序工作,或者可分别予以旁路,最终根据后续FPGA或ASIC(其采样速率较低)的要求,产生一个位于DC的复信号或一个实信号。

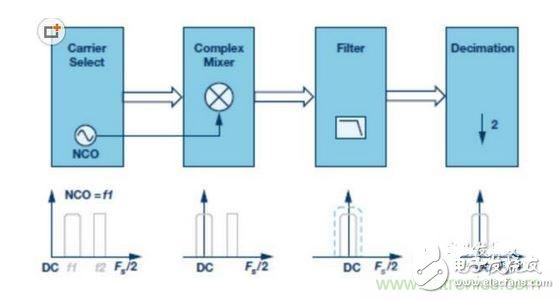

典型DUC模块包括插值、滤波器、上变频器和载波合并器。根据系统架构设计,DUC产生一个位于DC的复信号或中频信号,或者直接产生射频信号。DUC的处理几乎与DDC的处理相反。

常常将多个DDC和DUC级级联以提供灵活性。独立的DDC和DUC需要并行处理多个载波,合并之后输出发射信号或在接收信号中将其分离。

DDCRx链路需要较高采样速率以避免信号混叠,简化模拟滤波器设计,提供更宽的信号频带。但另一方面,为了节省功耗、成本以及FPGA/ASIC中的高速逻辑,最好降低接口上的数据速率。转换器的集成DDC将解决上述要求。图2是典型DDC的框图。

图2.DDC框图

NCO和混频器

为了从干扰(阻塞信号和其他载波)中选择所需的载波,NCO的输出频率与输入中频信号混频以将所需载波频移到DC。这样可以降低后续滤波和抽取级的复杂度。

滤波和抽取

在NCO和混频级之后,使用一个低通滤波器来选取所需的滤波并抑制其他不需要的信号。滤波器之后,使用一个2倍抽取器来降低数据速率。为了节省资源并向客户提供灵活性,半带FIR滤波器加2倍抽取器被合并在一个模块中;重复使用该模块以级联三到四级。系统设计者可根据应用需要选择使用其中的一部分或全部。转换器也可能提供2倍之外的其它抽取率以提供更大的灵活性,尤其是在RF ADC中。

DUCTx链具有与Rx链相同的要求:需要高采样速率以简化滤波器设计,使信号频率位于高中频或直接变为射频,以及远远地推开镜像,但接口希望使用较低的数据速率。转换器的集成DUC将解决这些要求。图3是典型DUC的框图。

插值和滤波

最简单的数字插值算法称为“零填充”,即在每两个样本之间插入0。采样速率加倍,但在得到的频谱中也会产生频率为Fs –Fif的镜像。因此,在插值器之后需要使用一个滤波器级,以便消除镜像或原始载波(依据应用而定)。如果消除的是原始载波,结果将是插值和Fs/2的粗调。

像在DDC中一样,2倍插值和滤波器被合并为一个模块。然后重复此功能模块并级联三到四级,以提高灵活性。也可使用2倍之外的其他插值系数以提供更大的灵活性,尤其是在RF DAC中。

NCO和混频器

DUC中的NCO和混频器级与DDC中的相同模块非常相似,但功能相反,即根据系统架构的要求,将载波频移到所需的中频或射频频率。在零中频架构中,可旁路此模块以使载波保持在DC。

增益、相位、I/Q偏移和反Sinc

增益、相位调整、I/Q偏移和反sinc模块是许多IF/RF DAC的附件。

增益、相位调整和I/Q偏移常常一起使用以独立调谐输出信号I/Q通道,补偿不同类型的I/Q失配(DAC、模拟滤波器和调制器引起),最终从模拟调制器后输出一个低本振泄漏和低镜像的理想复信号。

图3.DUC框图

反sinc滤波器补偿DAC引起的sinc滚降,这种滚降会影响平坦度和信号幅度,尤其是在采用高中频或直接射频架构的宽带应用中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)