红外密集度光电立靶测试系统是一种新型的用于测量低伸d道武器射击密集度的测试系统,既测试无须进行任何特殊处理的金属d丸,又可测试非金属d丸,更有反映灵敏、精度高而稳定、 *** 作简单、容易维护等优点,已被许多靶场投入使用。

光电靶的基本原理是:当光幕内的光通量发生足够大的变化时,光电传感器会响应这种变化而产生电信号。这就是说,一些非d丸物体在穿过光幕时也会使得光幕内光通量发生变化以至光电传感器产生电信号。从原理上,这种现象并非异常,而对测试来讲则属于干扰。在具体靶场测试中,当干扰严重时会导致测试根本无法进行。因此,如何排除干扰,保证系统的正常运行,是一个必须解决的问题。

理论分析光电靶在工作时,光电传感器响应光幕内光通量的变化,将其转变为微弱的电信号,经过放大后,进入电压比较器,当其幅值高于预定基准时,电压比较器翻转,产生触发脉冲。

由于随同d丸穿过光幕的细小物体和外界光线变化产生的信号幅值较小,通过对电压比较器设置合适的比较门限便可滤除这种信号。在靶厂实际测试中,这种干扰信号幅值一般小于0.8V,在电路中只要将电压比较器的门限电平设为0.8V便可消除这种干扰。

根据光电靶的工作原理,穿过光幕的飞行物体速度不同,遮挡光幕的时间就不同,在电路中表现为比较器后产生的方波脉冲的宽度不同。与d丸相比,蚊虫的飞行速度要低得多,当其穿过光幕时,产生的方波脉冲的宽度要比d丸产生得宽;在亚音速d测试中,d丸速度低于声速,由声波引起的脉冲宽度小于d丸产生的方波脉冲宽度。因此,从原理上在比较器后利用滤波电路滤除干扰信号是可能的。

利用FPGA实现滤波及抗干扰整个电路的主要功能是抗冲击波和蚊虫干扰,并把有效d丸信号变成脉宽为50μs的信号输出到下级处理电路。设计中采用的芯片是MAX7000系列的EPM7128SLC84-15芯片。下面就如何实现滤波和抗干扰作详细介绍。

1 电路原理当有物体穿过光幕时,所产生方波的脉冲宽度为:T=(L+D)/V。式中,L为飞行物的长度,D为光幕面的厚度,V为飞行物的速度。冲击波以声速计算,V为340m/s,D=3mm,则可知冲击波穿过光幕产生的方波信号脉冲宽度为:T1=D/V≌8.8μs;若V=330m/s,则T1≌9.1μs。蚊虫等飞行物飞行速度V为20m/s,物体长度L大约为10mm,则可知蚊虫飞过光幕产生的方波信号脉冲宽度为T2≌650μs。红外密集度立靶测试系统测试d丸d速范围为200~1200m/s,主要用于5.8mm、7.62mm、9mm三种d;冲击波的影响主要产生于对9mm×19mm的手qd的测量,该d丸d速约为320m/s。根据d速和d长,可知d丸穿过光幕产生的方波信号脉冲宽度范围为T3=37.5μs。

根据靶场实际测试情况,d丸穿过光幕时产生的方波信号脉冲宽度基本都小于150μs且大于10μs,则可以认为脉冲宽度大于150μs小于10μs的信号为无效信号,可以剔除,此时可将蚊虫干扰信号和冲击波信号滤除,达到抗干扰的目的。

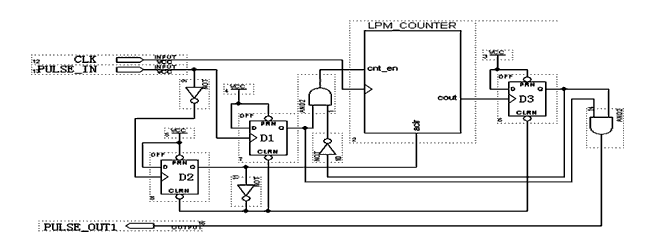

2抗冲击波电路

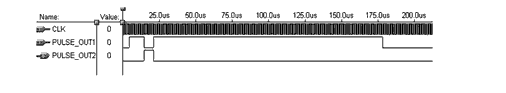

滤除冲击波电路如图1所示。当PULSE_IN端出现一个正跳变时,上跳沿使得触发器D1的输出端产生高电平信号,则启动计数器开始计数。当计数器计满后,计数器输出端产生一个正跳变,上升沿使得触发器D3的输出端产生一个高电平信号,将这两个信号相与得到输出信号PULSE_OUT1。当PULSE_IN的下降沿到来时将计数器和三个触发器同时清零,等待下一个信号到来。由图2可知,当PULSE_IN的脉宽小于设定计时宽度时,认为干扰信号PULSE_OUT1为低;当PULSE_IN的脉宽大于设定计时宽度时且仍为高时,认为信号有效,PULSE_OUT1为高且在PULSE_IN的下降沿变为低电平,等待下一信号的到来。

图1 滤除冲击波电路

图2 抗冲击波电路仿真波形图

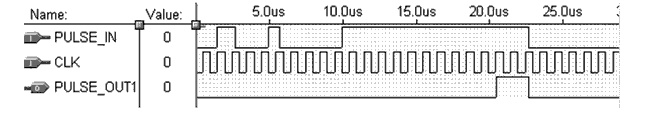

3 抗“蚊虫”干扰电路

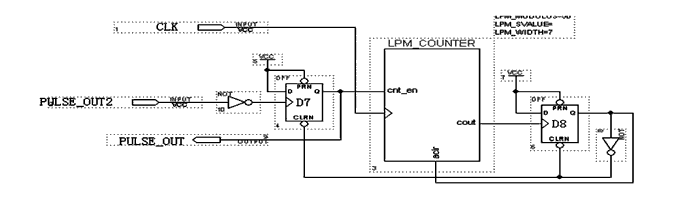

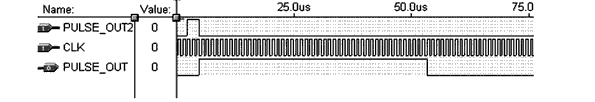

当PULSE_OUT1有一个正跳变时,计数器开始计数,若计数器计满则计数器cout端将有一个正跳变,经反相后加在触发器D4的Q输入端。在PULSE_OUT1的下降沿到来时,触发器D4的输出端仍输出低电平信号,输出信号PULSE_OUT2为低,即若PULSE_OUT1的脉冲宽度不小于计数器计时宽度时,PULSE_OUT2端将输出低电平信号;若计数器未计满则cout 端将不会有上升沿,触发器D4的Q输入端为高,在PULSE_OUT1的下降沿使触发器D4的输出端为高时,输出信号PULSE_OUT2为高。在PULSE_OUT1上升沿到来时,触发器D6的输出端输出为高经反相器后将触发器D4和D6同时清零,等待下一信号的到来。

4 脉宽设定电路

为了保证d丸穿过光幕产生的脉冲信号能够非常适合后续处理电路的需要,在设计中将d丸穿过光幕产生的脉冲信号均变为脉宽为50μs的脉冲信号再输出给后续电路。

当PULSE_OUT2有一个正跳变时,触发器D7的输出端输出高电平,并启动计数器。当计数器计满时,计数器cout出现上升沿,触发器D8的输出端输出高电平,此高电平信号将计数器清零,同时经反相器反相后接到触发器D7和D8清零端,将触发器D7和D8清零。

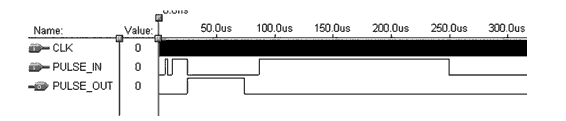

整个电路的作用就是,当PULSE_IN上跳沿到来后,先经过抗冲击波电路,若信号脉宽大于10μs,则启动抗蚊虫干扰电路;若信号脉宽大于150μs,输出PULSE_OUT为低电平信号;若脉宽小于150μs,则经过脉宽设定电路变成宽度为50μs的信号输出。

通过分析可知应用FPGA器件所设计的抗干扰电路具有可灵活调节信号的脉宽修改方便、对输入信号的脉宽适应能力强可调节范围大、输出的脉冲宽度和幅值稳定准确的特点。

图3 抗蚊虫干扰电路

图4 抗蚊虫干扰电路仿真波形

图5 脉宽设定电路

结语

为了在测试d丸射击密集度时消除冲击波和蚊虫干扰,利用FPGA器件来设计抗干扰电路,本电路简单可靠,能有效地消除干扰脉冲,从而保证了数据的准确性和可靠性。

图6 脉宽设定电路仿真波形图

图7 整体电路仿真波形图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)