作者:Steve Leibson, 赛灵思战略营销与业务规划总监

你想对FPGA、NPU和多核CPU在包处理中的优缺点有个清晰认识吗?在圣克拉拉的Linley Processor Conference 2014上赛灵思的AtulShinde发表了“为最佳载体以太网处理分离硬件和软件可编程性”的演讲,讨论了这个话题 。

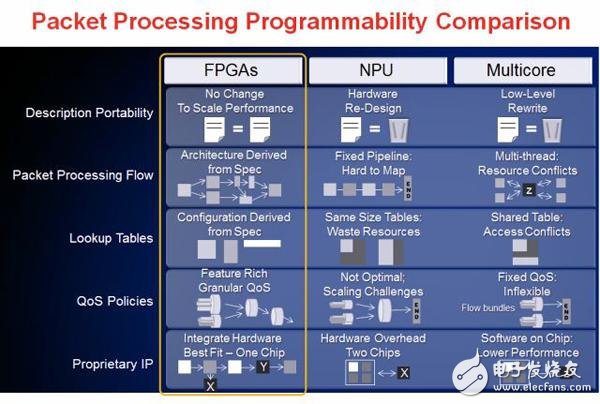

Shinede的幻灯片例举了5个主要方面进行比较:

描述可移植性:你面临额外的工作如果你需要改变系统描述来适应实现硬件。

包处理流:如果实现硬件不能满足包处理要求的自然流,你会面临瓶颈和资源冲突

查找表:实现硬件的固定大小内存会导致资源浪费和访问冲突

QoS策略:糟糕的执行力会导致次优化缩放和灵活性缺失。

专有IP:如果你需要特殊的包处理,你会承担额外的硬件或者忍受使用NPU或者多核CPU进行基于软件处理的不高效

原文链接:

? Copyright 2014 Xilinx Inc

如需转载,请注明出处

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)