1 概述

在各种锁相环结构中,电荷泵锁相环因其稳定性高,捕获范围大,便于集成等特点而别广泛应用于无线通信、频率综合器和时钟恢复电路中。随着芯片设计集成化和电路设计的简洁化,锁相环芯片通常都集成了环路锁定检测电路。

电荷泵锁相环的锁定检测电路设计,包括模拟锁定检测和数字锁定检测两种方法。其中,模拟检测电路采用经鉴频鉴相器PFD 输出的相位误差,产生脉冲信号对外部电容进行充电和放电,需要较长的时间以达到稳定的电平输出,以指示当前锁相环状态是锁定或失锁,在电路设计方面不够灵活并缺乏精确判断锁相环的锁定状态,限制了其应用范围。数字锁定检测方法具有准确性高、可编程性且电路设计易于实现等优点而被广泛应用。目前,电荷泵锁相环的数字锁定指示电路设计中,通常采用在鉴频鉴相器PFD 电路中检测经过分频后的参考时钟输入和同样经分频后的本振反馈信号的相位误差来实现,当相位误差超过某个锁定检测窗口时,锁相环电路就上报失锁指示信号。本文介绍了电荷泵锁相环电路锁定检测的基本原理,通过分析影响锁相环数字锁定电路的关键因子,推导出相位误差的计算公式。并以CDCE72010 为例子,通过实验验证了不合理的电路设计或外围电路参数是如何影响电荷泵锁相环芯片数字锁定指示的准确性。

2 电荷泵锁相环电路的数字锁定检测原理

相位误差是数字锁定检测原理的最关键参数,下面分析了电荷泵锁相环电路中相位误差的来源,以及数字锁定检测电路是如何基于相位误差实现的。

2.1 PFD、电荷泵电流和相位误差

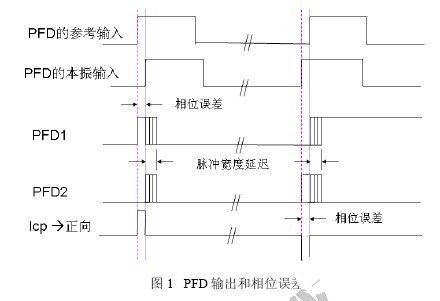

典型的电荷泵锁相环电路(如TI 的CDCE72010)的PFD 工作原理如图1 所示。当送达PFD 的参考

时钟输入超前本振时钟输入时,PFD1 就输入一个高脉冲宽度的信号;反之,则在PFD2 输出一个高脉冲电平宽度,通过PFD1 和PFD2 的脉冲信号以控制电荷泵电流的灌入和流出,经后级低通滤波器后,产生不同的压控电压以控制外部振荡器的输出,达到负反馈的稳定。通常PFD 电路是通过比较参考时钟和本振时钟上升沿之间的时延,该时延称之为相位误差。在电路处于锁定状态时,该相位误差也就是锁相环的稳态相差参数。

2.2 数字锁定检测原理

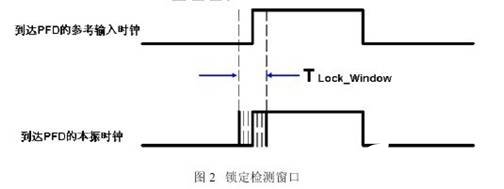

数字锁定检测的基本原理就是比较相位误差和预先设定的锁定检测窗口TLock_Window,一旦相位误差在连续N 个周期里均落在预先设定的检测窗口以内,数字检测电路就指示该锁相环处于锁定状态;而在锁定状态下,一旦相位误差超出所设定的检测窗口,数字检测电路就指示该锁相环处于失锁状态。

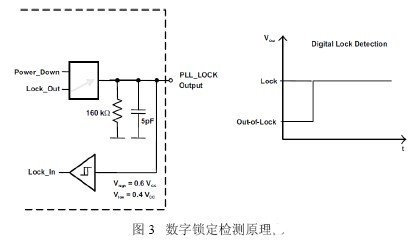

图3 是CDCE72010 器件数字锁定检测电路示意图,当CDCE72010 处于锁定状态时,锁定指示信号PLL_LOCK Output 输出为高电平。其中,N 的取值可以是1、16、64 或256,锁定检测窗口可选范围很宽,从1.5ns 到28.6ns(常温条件下),可以满足绝大多数应用场合的需求。

3 数字锁定电路设计

由于数字锁定检测电路是通过分析锁相环的相位误差是否落在预设的锁定检测窗口范围进行锁定指示判断,而锁相环的应用场景复杂,实际应用中的电路设计差异性较大,相位误差参数受锁相环电路设计的影响较大,不恰当的电路设计和外围器件选型可能产生较大的相位误差并超出锁相环芯片的最大锁定检测窗口。因此,需要根据特定锁相环配置和外围电路选择合适的检测窗口,或者根据检测窗口要求设计合适的锁相环环路参数和外围电路。本节分析了影响锁相环锁定时相位误差的关键参数,重点探讨了如何可靠地设计数字锁定指示电路。

3.1 电荷泵锁相环电路锁定状态下的相位误差分析

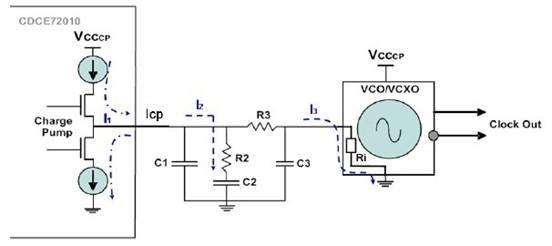

图4 是基于CDCE72010 的电荷泵锁相环电路漏电流模型,包括了无源滤波电路和本地压控振荡器VCO 或VCXO。理想情况下锁相环电路的相位误差应为0,但由于元器件的非理想特性,存在以下几种漏电流:电荷泵漏电流I1、滤波电路的电容C1、C2 和C3 引入的漏电流I2 和本地压控振荡器引入的漏电流I3,这些漏电流(I1 + I2 + I3)均将影响环路锁定状态下的相位误差。

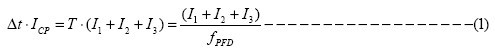

当锁相环处于锁定状态时,设相位误差为Δt,电荷泵输出脉冲宽度为Δt 幅度为Icp 的电流,则在一个鉴相周期T 内在后级低通滤波电容上积累的电荷量为Q1=Δt• Icp。同时,在一个鉴相周期内,锁相环电路的漏电流泄漏的电荷为Q2 = T• (I1+I2+I3)。锁定状态下的压控电压保持稳定,则经电荷泵补充的电荷Q1 应等于漏电流泄漏掉的电荷Q2,即:

其中, ![]() 为锁相环电路的鉴相频率。

为锁相环电路的鉴相频率。

图4 CDCE72010 电路中影响相位误差的漏电流模型

在图4 所示的漏电流模型中, I1 是锁相环芯片引入了,CDCE72010 的电荷泵漏电流指标是小于100nA,目前普通陶瓷电容的漏电流I2 也远小于100nA,而压控振荡器的漏电流I3 则可以等效为流过压控输入端输入阻抗的电流,不同规格的振荡器,该指标差异较大,通常是达到uA 级别。因此,压控振荡器的等效输入阻抗参数是影响锁相环锁定下相位误差的关键来源。

在采用CDCE72010 的锁相环电路中,通常采用电源电压为3.3V 的压控振荡器VCO/VCXO,其锁定时的压控电压Vctrl 一般稳定在1.65V 附近。根据式(1),若忽略I1 和I2 漏电流,则在锁定状态下由VCO/VCXO 输入阻抗引入的相位误差为:

![]()

根据式子(2)可以看出,为了减小锁定时的相位误差,可以尽可能地提高锁相环的鉴相频率f PFD 、电荷泵电流Icp、以及压控振荡器的输入阻抗Ri。

3.2 数字锁定检测电路设计和实验测试

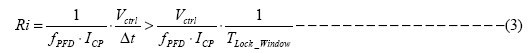

在数字锁定检测电路设计中,必须严格确保锁定时的相位误差Δt 小于锁定检测窗口TLock_Window,

否则数字锁定指示信号就将出现误判现象。根据前面分析得知,在CDCE72010 锁相环电路中,外部VCXO 的输入阻抗是数字锁定电路设计的一个关键参数,根据式(2),可以得到压控振荡器输入阻抗的指标要求:

假设在应用中CDCE72010 中鉴相频率为1MHz,电荷泵电流为1,预设的锁定检测窗口为5.8ns,本地VCXO 的压控电压为1.65V,则可以得到VCXO 的输入阻抗要求:

![]()

在锁相环电路设计中,鉴相频率和电荷泵电流与环路直流增益成正比,跟锁相环的环路带宽和相位裕量密切相关,为了得到较小的环路带宽,通常需要降低鉴相频率或电荷泵电流。进一步分析式(2),相位误差跟鉴相频率和电荷泵电流成反比,因此在低环路带宽电路的设计中,必须特别注意压控振荡器的输入阻抗(或漏电流指标)和锁定检测窗口的设计,严格满足式(3)的设计要求。

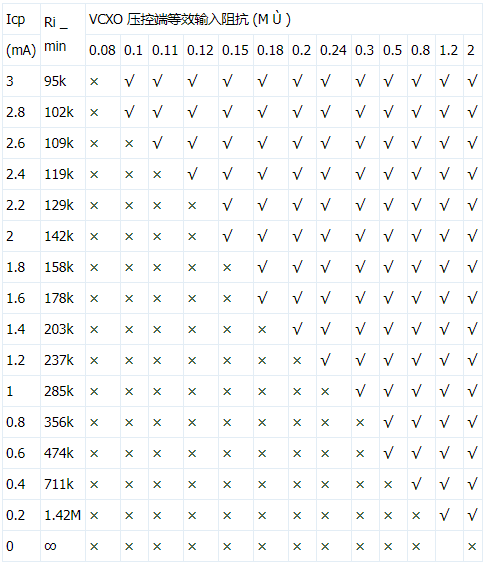

可以通过实验来检查式(3)的正确性。在CDCE72010 的评估板上,改变VCXO 压控端的等效输入阻抗,通过观察CDCE72010 锁定指示输出管脚或锁定指示寄存器的锁定状态,分析该锁定检测电路是否可靠地工作,具体实验设置如下:

参考时钟为25MHz,VCXO 频率为125MHz,鉴相频率为1MHz,PFD 的检测窗口为5.8ns,控制电压为1.65V,实验结果如表1 所示,其中R i _ min为计算出的VCXO 输入阻抗的最小值,√表示锁相环指示锁定,×表示锁相环数字锁定指示为失锁状态。其中,在实验过程中,由示波器监控CDCE72010 的参考时钟和本振时钟一直处于锁定状态。

表1 不同VCXO 输入阻抗值对CDCE72010 数字锁定指示的影响

从表1 中可以看出VCXO 的输入阻抗对锁相环的数字锁定有很大的影响,例如当电荷泵电流为1.2mA 时,根据式(3)可以得到VCXO 的最小输入阻抗为237Kohms,那么对于低于这个值的输入阻抗,数字锁相指示无法正确指示锁定,实验测试的结果与理论分析是吻合的。

4 总结

本文在电荷泵锁相环数字锁定检测工作原理的基础上,分析了影响锁定时相位误差的环路参数和外围元器件的关键参数,包括电荷泵电流、鉴相频率和漏电流等。同时根据对整个环路漏电流路径的分析,重点分析了外部压控振荡器的等效输入阻抗对锁相环锁定指示准确性的影响。

以CDCE72010 数字锁定设计为例,为了提高数字锁定检测电路锁定状态指示的准确性,在低环路带宽的锁相环电路设计中,必须选择恰当的外部压控振荡器的输入阻抗参数指标。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)