近年来,云计算和大数据应用呈爆发式增长,在推动数据中心产业升级的同时,也为数据中心的应用开发与运行维护带来了一系列问题。目前,数据中心运维人员主要通过易于编程的多核CPU和GPU来开发应用,但CPU 和GPU 都遇到了单位功耗性能的瓶颈壁垒。而从事海量数据中心应用开发(如密钥加速、图像识别、语音转录、加密和文本搜索等)的设计人员则既希望GPU 易于编程,同时又希望硬件具有低功耗、高吞吐量和最低时延功能。然而,多核CPU和GPU 加速在可扩展性上存在严重的问题,即客户希望用简单的全高度插入式PCIe 开发板作为数据中心服务器的应用加速。这种开发板经配置可运行高功率图形卡,但客户同时希望功耗不超过25W,以便最大化可扩展性并最小化总功耗。

面对这些苛刻的需求,在比较了GPU、DSP、FPGA等多种方案之后发现,同等物理环境中,FPGA在降低功耗和提升性能上表现最佳。但将FPGA应用于数据中心存在一个最大的问题——编程。数据中心应用开发人员不希望采用传统FPGA的开发路径,即以硬件为中心的RTL流程,他们希望能够在完全软件的开发环境中完成易于升级的设计,同时保证单位功耗性能最高。

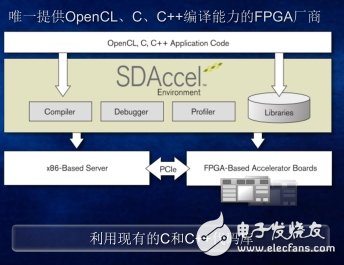

Xilinx在2014国际超算大会上推出的针对OpenC++L、C和C++的SDAccel开发环境完美地解决了这一难题。作为首款面向FPGA 平台的完全软件的开发环境,SDAccel带有用于代码开发、特性分析与调试的Eclipse 集成设计环境,可提供类似于CPU/GPU 的工作环境。开发者可以像在CPU/GPU系统中一样管理和运行基于SDAccel的系统。不仅如此,CPU/GPU开发人员还能够轻松地将其应用迁移到FPGA上,同时还可在他们熟悉的工作流程中维护和复用OpenCL、C和C++代码。

“相比CPU/GPU实现方案,基于FPGA的应用加速其单位功耗性能可提升25倍,而时延则缩短了50~75倍。”赛灵思公司亚太区销售与市场副总裁杨飞强调。这得益于SDAccel的架构优化编译器,这也是行业首款面向C、C++和OpenCL的架构优化编译器。借助该编译器,开发者可高效利用片上FPGA资源,优化并编译流媒体、低时延以及定制数据路径应用。

SDAccel 为数据中心应用开发人员提供了完整的FPGA软硬件解决方案。开发人员能用熟悉的工作流程优化应用,而且即便很少或者没有FPGA 使用经验,也能获益于FPGA 的平台优势。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)