因为MicroZed是个低成本的开发套件,所以在板子上除了给PS(33.3333 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供时钟信号外,并没有为PL部分提供单独的晶振。为了让PL部分正常工作,一种方法是使用接口板从外部输入到PL的管脚上一个时钟信号,另一种方法则是使用PS提供给PL的时钟信号。

从ZYNQ的技术手册里我们得知,PS部分可以提供给PL四路相对独立的时钟信号(它们之间不保证时序上的关系),因此我们的任务就是配置PS和PL,把这些时钟信号利用起来。此时我们就可以充分利用Vivado提供的强大的集成开发功能,轻松实现PL“打包”PS的功能——这与通常我们看到的ZYNQ的概念有点不同:PS是主体,而PL做为一个逻辑胶合者被PS指挥;当然上电和初始化顺序还是一样的,必须先启动配置完PS,才能初始化PL。

首先我们在Vivado开发环境中建立RTL工程,并编写我们需要在PL中实现的功能代码HDL文件,把它做为顶层文件。

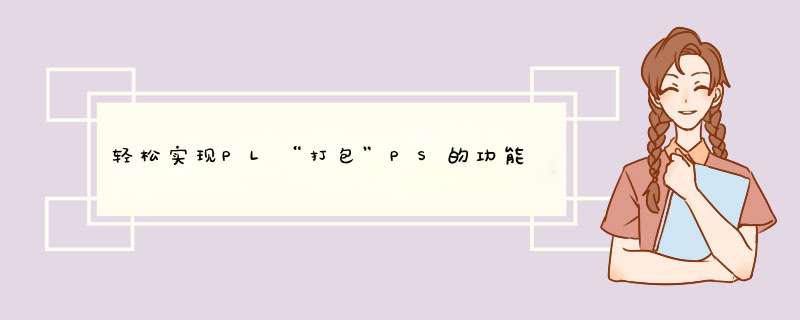

然后我们调用PS的IP核,建立并配置一个PS。如果不清楚这个过程的网友,请参考,然后我们配置PS到PL的时钟输出,如图1所示。

图1 配置PS到PL的时钟

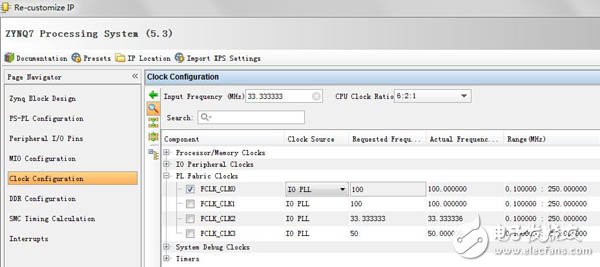

然后我们在管脚上点击创建端口,如图2所示。

图2 创建PS端口

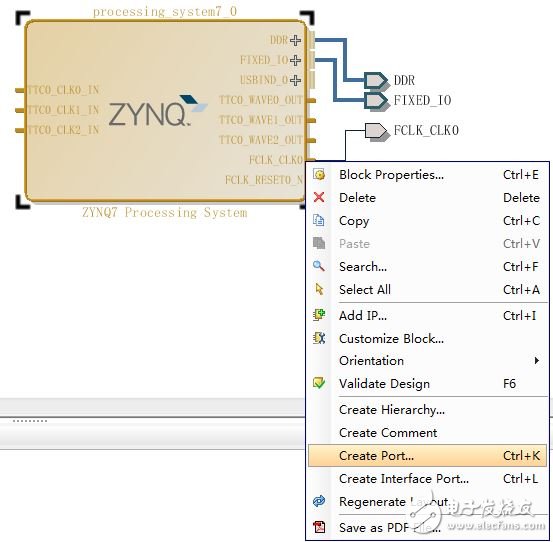

点击Run AutomaTIon,可以看到创建成功的PS和它的端口连线,如图3所示。

图3 PS端口与连线

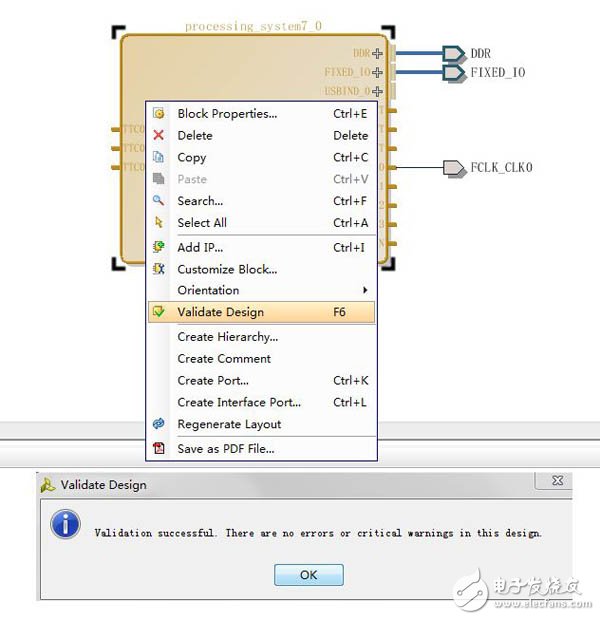

然后在PS上点击右键,进行基本的设计验证,如图4所示。

图4 验证设计

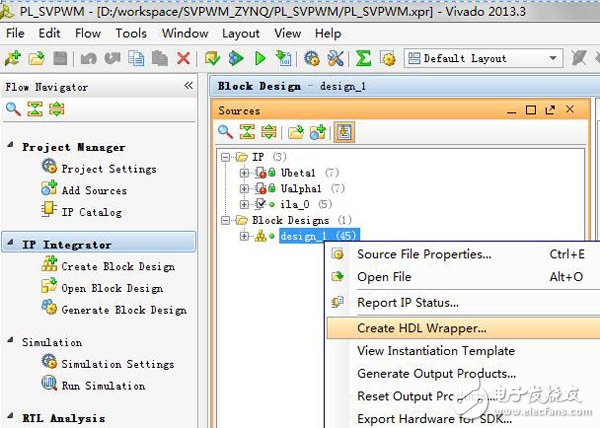

完成了PS的配置之后,我们在工程管理器里对生成有关PS的打包文件,这是一个HDL文件,如图5所示。

图5 生成HDL打包文件

接下来的事情就容易理解了:把PS及其端口、连线等一起生成的打包文件HDL文件,在我们开头创建的顶层HDL文件里面进行例化。如果需要调用IP核的话,我们既可以在图3之前的步骤里面直接用IP Integrator创建然后直接把PS的端口和IP自动关联,然后生成HDL打包文件后在顶层文件里面一起例化,也可以直接在顶层文件里面进行IP核的例化,当然前一种方式更方便,因为图形化的方式更直观、快捷。

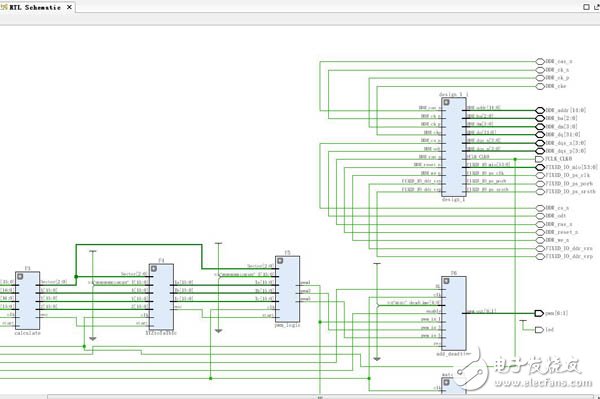

结合,可以看到PS部分已经被我们的顶层文件正确调用了,查看此时的RTL如图6所示。

图6 PL中顶层文件的RTL

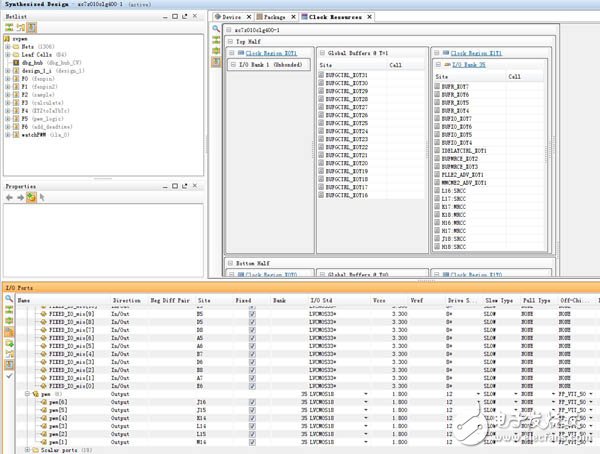

此时我们对比没有PS的设计,可以看出实现后的结果的区别了,如图7、图8所示。

图7 没有PS的实现结果

图8 例化了PS的实现结果

此外,需要补充的一点是,在我们的顶层文件里面对PS的打包文件进行例化的话,需要定义许多与PS有关的端口做为输入、输出或者双向端口,这样在设计文件中会产生上百个甚至更多的管脚。幸运的是,Vivado会自动为PS相关的端口分配管脚并设置电平标准,所以我们只需要对PL部分我们的程序分配管脚并设置电平标准就行了,如图9所示。

图9 自动分配的PS管脚

既然PL中也有时钟信号了,那么在完成PS的初始化之后,就可以对PL中的信号进行在线调试了,请看后续博文。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)