我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及性能数据,提出对参考时钟的相位噪声的具体要求。这个要求,通常是以不降低其SERDES性能为依据的,一般情况下较严。那么,是不是一点也不能违背呢?作为供应商,总是希望有较好的参考时钟,这样系统余量最大。但作为用户,总是希望用便宜的参考时钟,满足需要并有一定余量就行。这就要求在工程实践中作某种平衡,你需要对系统指标要求,SERDES性能有非常清楚的了解。

比如:XILINX 7系列SERDES的CPLL对参考时钟的相位噪声要求如下:

Ref Clock Freq (MHz)

Phase Noise at Offset Frequency ? (dBc/Hz)

10KHz

100KHz

1MHz

100

-126

-132

-136

125

-123

-131

-135

156.25

-121

-129

-133

250

-119

-126

-132

312.5

-116

-124

-131

625

-110

-119

-127

用户设计需要跑XAUI协议,由于XAUI接收机的CDR的抖动容限拐点大约在1.87MHz。因此,参考时钟的1MHz以下的相位噪声可以适当放宽。

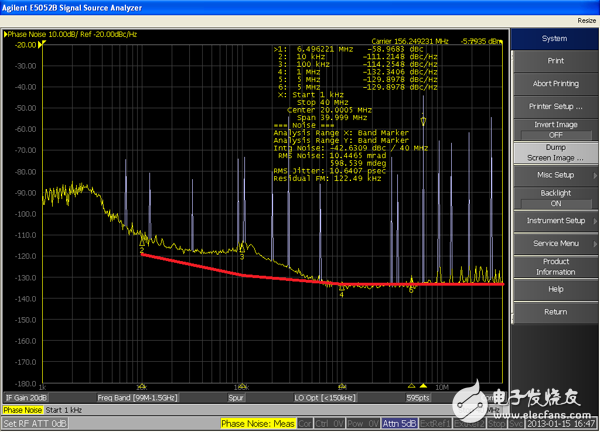

Case 1:

参考时钟的相位噪声在1MHz以下已经不满足模板的要求,但1MHz以上本底噪声有较大余量,很少的杂散有少量超标。这是可以接受的,并且在工程实践上,也是成功的,全面满足了用户的系统要求。

Case 2:

参考时钟的相位噪声在1MHz以下已经不满足模板的要求,且1MHz以上本底噪声也没有余量,杂散严重超标。这是不可以接受的,并且在工程实践上,也造成了收发两个方向上的误码。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)