12.2.6 PicoBlaze输入/输出端口

PicoBlaze微控制器支持最大256个输入口和256 个输出口,PicoBlaze与输入和输出有关的信号在“PicoBlaze微控制器接口信号”部分有详细说明,包括PORT_ID[7:0]、IN_PORT[7:0]、OUT_PORT[7:0]、READ_STROBE WRITE_STROBE。在时序要求苛刻的设计中, 对PORT_ID 和数据路径允许两个时钟周期, 对于READ_STROBE 和WRITE_STROBE 需要约束到一个时钟周期。为了提高性能,在允许的情况下可以插入流水寄存器。

PORT_ID:此信号作为输入或输出端口的标识或者说是地址。它的有效高电平持续两个时钟周期,这样做的目的是为了有足够的时间进行译码,有足够的时间与异步RAM 连接,还有,在双周期 *** 作时,允许从同步RAM(例如,BRAM)中读数据。

INPUT 和OUTPUT *** 作支持直接和间接寻址,端口地址由立即数指定或由寄存器指定。间接寻址方式适用于对BRAM、具有连续地址的外设、片内或片外存储器中的表格的访问。

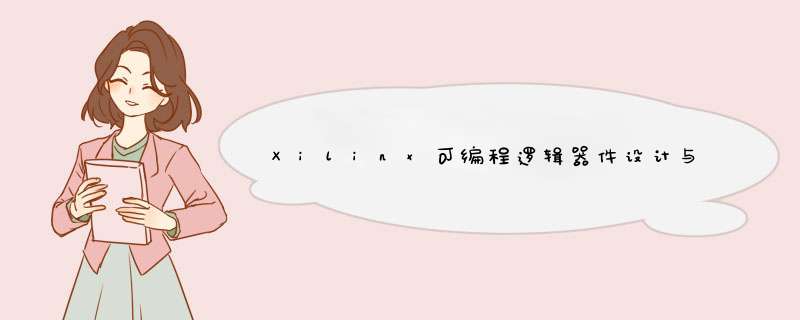

扩展PicoBlaze 外设其实非常方便,唯一具有挑战性的地方在于,如何用最少的逻辑资源实现对PORT_ID 译码。表12-2 所示为一般的方法(取决于端口数)。

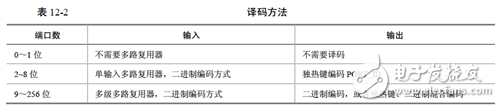

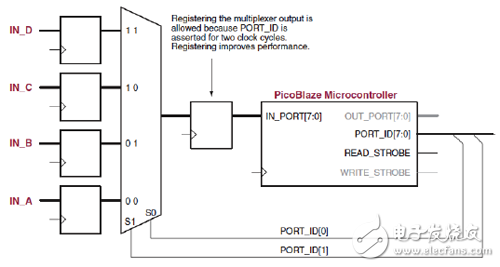

输入 *** 作将IN_PORT输入口的数据传送到由寄存器sX 指定的16 个数据寄存器中的任何一个,如图12-11所示,PORT_ID 由sY确定或者由一个8位的立即数确定,指定输入源。输入源由一个多路器选择,多路器的大小与输入源的通道数成正比,它直接影响PicoBlaze 的性能。

图12-11 输入 *** 作和FPGA内部接口

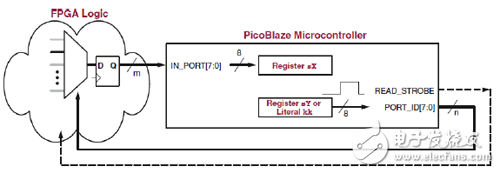

图12-12中为输入指令时序图,图中显示PicoBlaze微控制器从由s7指定的端口读数据,数据被读入s0。当执行此指令时,寄存器s7 的内容出现在PORT_ID上,PORT_ID被FPGA内部逻辑译码,被请求的数据出现在IN_PORTREAD_STROBE 在输入指令的第二个时钟周期变高,尽管READ_STROBE 主要用于FIFO,以使FIFO 能够更新它的读指针。出现在IN_PORT的数据在第2 个上升沿被采样,表明INPUT指令执行完毕,之后,数据被采样进入s0。

图12-12 INPUT 指令的PORT 时序

从图12-12时序图可以看出,由于PORT_ID保持两个时钟周期有效,所以输入数据多路器可以被寄存,以保证性能,如图12-13所示。

图12-13 由多路器将多个输入变为一路输入

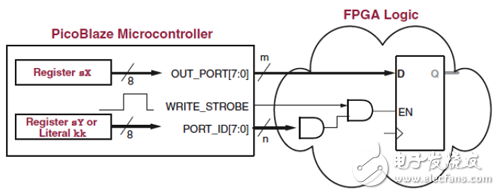

二、 OUTPUT *** 作输出 *** 作将寄存器sX 的内容送到OUT_PORT,PORT_ID 由寄存器sY 确定或者由一个8位的立即数确定,指定输出口。WRITE_STROBE 表明OUT_PORT 数据有效,并且准备好被捕获。通常情况下,WRITE_STROBE 与PORT_ID 组合成时钟使能或者写使能供FPGA逻辑捕获输出数据。

图12-14 OUT_PORT与FPGA逻辑

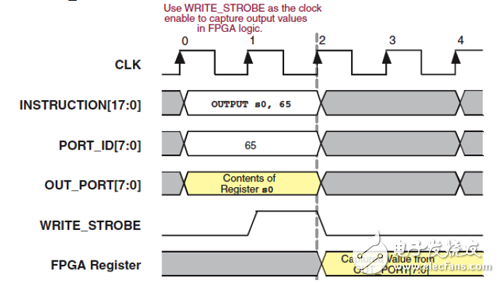

图12-14是一个扩展输出端口的实例,图12-15为其时序图,PicoBlaze 要将s0的内容送到PORT_ID为65HEX 的端口,s0 的内容出现在OUT_PORT,端口地址65HEX 出现在PORT_ID,WRITE_STROBE 在指令周期的第二个时钟边沿变高,表明数据有效。

图12-15 OUT_PORT 指令的PORT 时序

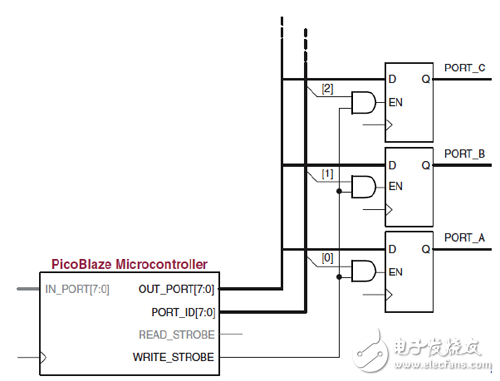

对于8个或者少于8个的输出口,常用one-hot编码方式,如图12-16所示,因为它仅需要对PORT_ID的某一位进行译码,所以很大程度上减少了FPGA译码逻辑所需资源,同时也提高了性能。如果用来译码的PORT_ID位数为3或者小于3,则译码逻辑仅用一级逻辑即可实现,这时的性能最高。

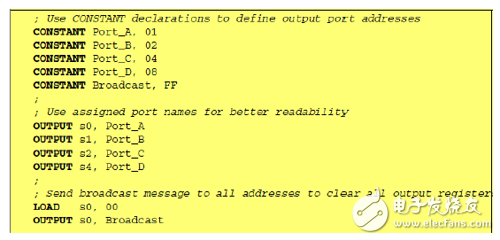

图12-17所示为一个简单的输出程序,用one-hot编码定义4个输出口,同时定义了一个广播式的输出口,先向4个输出口输出4个不同的值,最后两条语句将所有4个口清零。

图12-16 简单的输出

图12-17 one-hot 编址输出例程

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)