S2C日前宣布其VerificaTIon Module技术(专利申请中)已可用于其基于Xilinx的FPGA原型验证系统中。V6 TAI VerificaTIon Module可以实现在FPGA原型验证环境和用户验证环境之间高速海量数据传输。用户可以使用Xilinx ChipScope或者第三方调试环境,同时查看4个FPGA。另外,V6 TAI VerificaTIon Module还可以用于1.3M~4.7M ASIC门的原型设计。V6 TAI VerificaTIon Module具有PCIe Gen2、千兆串行收发器、SATA2和USB 3.0等高速接口。V6 TAI Verification Module硬件现已供使用。

S2C的董事长及首席技术官Mon-Ren Chene先生说:“我们在今年6月份首次发布的Verification module技术是为使用Xilinx原型验证系统的客户提供的技术。这是一种可以将用户的FPGA原型环境和用户验证环境接口的突破性技术。由于设计通 常被分割到多个FPGA中,用户可以有这项新能力同时对多个FPGA进行调试对他们来说非常重要。FPGA原型验证系统以系统速度或者接近系统速度运行。 通过高速接口,FPGA原型验证环境可以更容易地连接到实际目标系统环境。”

三种运行模式

通用的S2C V6 TAI Verification Module提供了三种使用模式:验证模式、调试模式和逻辑模式。 验证模式使用SCE-MI或定制的C-API通过一条 x4-lane PCIe Gen2通道实现海量数据和PC之间的传输。在调试模式中,V6 TAI Verification Module通过使用Xilinx ChipScope或者其它第三方工具从而实现了多个FPGA的同步调试且同时保持用户的RTL名。在逻辑模式中,用户可以原型化一个设计,其容量能达到 4.7M门。 所有对Verification Module的调试和验证设置都是在S2C 的TAI Player Pro™中完成。

验证模式

验证模式利用TAI Verification Module的高速PCIe Gen2接口将大量仿真数据在PC和TAI Logic Module之间进行双向快速地传输。该模式能将原型系统和仿真器直接连接进行同步仿真。用户可以利用下图所示的S2C提供的定制C-API或者符合行业 标准的SCE-MI接口:

调试模式

调试模式则利用了用户现有的Xilinx ChipScope或者其它第三方调试环境。V6 TAI Verification Module从Logic Module中的多个FPGA获取用户定义的信号并接收到V6 TAI Verification Module,通过JTAG接口与ChipScope连接。

V6 TAI Verification Module 使用Xilinx ChipScope Analyzer可同时对放在两块Dual V6 TAI Logic Module上的FPGA设计进行调试。

最高能见度

每个Virtex 6 FPGA的120信号都接到了V6 TAI Verification Module的FPGA中。用户能在4 个V6 FPGA中进行120 x N信号的路径选择。最初的发布中,N固定在4上,但今后将由用户定义。用户所需要做的是在设计综合前在RTL级选择Probes并且将它们按照每个 FPGA120个probe来进行分组。S2C的TAI Player Pro自动采用多路复用技术将来自多个FPGA的调试信号发送至V6 TAI Verification Module的单个Xilinx ChipScope,并保留RTL名。将使用Xilinx ChipScope调试过程中的调试数据存储在V6 TAI Verification Module的存储器中直到满足预先设置的触发条件为止,再将这些调试数据读取出来。

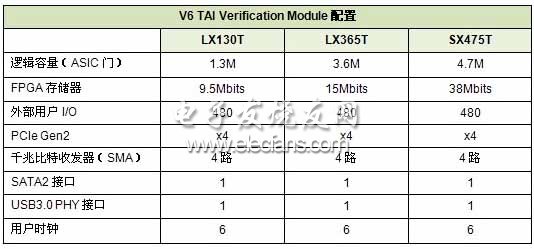

逻辑模块

配置详情显示在下表:

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)