越来越小的利润空间正驱使元器件制造商降低生产成本,包括测试成本在内。采用具有嵌入式测试排序器的仪器会起到作用。为了采取更有效的测试手段来提高利润空间,制造商要考虑新的测试范例以及构建测试系统的方法。在许多情况下,可以利用新的测试技术和仪器降低系统及测试 *** 作成本,改善现有测试台的性能。新一代具有先进的嵌入式测试排序器和数据通信能力的SMU(源测量单元)能够实现这一点。

SMU具有的这些功能容许建立紧凑并且经济的系统,进行快速的多通道元器件测试。随着测试要求的改变,它们也具备很高的灵活性,可以快速和方便的加以修改。采用这些仪器设计的系统可以在生产周期中更早地承担更多的测试任务,并帮助降低生产线末端测试的高昂成本。

典型的测量要求

首先,创建适合不同元器件制造商需要的基于仪器的系统看起来不切实际。DUT(被测器件)可能是简单的2引脚或4引脚器件,如二极管、 LED或三极管。这些测试都需要非常简单的源测量程序,要具备快速的瞬时响应,以在两个通道上生成精确的I-V曲线。由于元器件 *** 控的速度很快(某些情况下达到每部件小于100毫秒),因而仪器速度至关重要。

对于像电阻和RC网络、多引脚瞬态电压抑制器、EMI滤波阵列这样的元器件,在一个阵列获得通过之前,所有的单个元器件都必须通过测试。因此,需要并行的多通道测试以实现高的吞吐量。

随着元器件复杂性的增加,测试和通道的数量也需要增加。对于半导体器件,测试设备应该能够适合晶圆级测试,因为封装成本高昂。在生产的初级阶段,需要在纳安级别对各种复杂低功率器件的静态和泄漏电流进行测量。此外,需要对晶圆上的所有DUT进行简单的直流测量以检查基本功能。因为每一个晶圆存在成千上万个的DUT,所以必须采用快速多通道的测试。

在所有这些元器件生产的过程中,一种常见需要就是利用一组重复的测试序列向DUT施加电压或电流,测量其响应,将测量结果与可接受的极限进行比较,并作出合格/不合格决策。SMU的基本设计使它们非常适合于这类测试。然而,生产测试工程师需要仔细考虑仪器和测试系统架构中的差异,以针对当前的任务选择最佳的测试仪器,并设法预测将来的测试需要。

对于多DUT测试或对更复杂器件的多通道测试,要采用并行通道的I-V系统来提高测试吞吐量。尽管如此,测试速度可能仍然受限于仪器、应用程序或DUT稳定时间。现有并行通道系统的限制包括连续通道跳跃(即不能同时对所有并行通道进行测量)、测量量程变化的速度慢以及数据通信速度低。

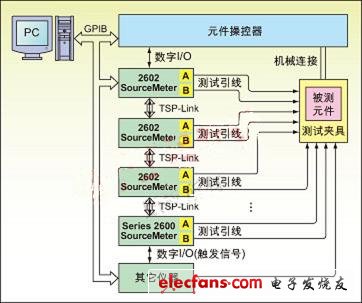

可扩展多通道系统针对更为复杂的元器件和测试场景进行设计。它们常常包括针对各种测试功能的不同仪器。SMU常常是一个核心组件,宽带仪器(信号发生器、示波器、频谱分析仪等)往往在外部添加。两种最为常见的架构是集成的功能测试仪和具有开放API(应用编程接口)仪器的I-V测试系统。

开放API意味着要把独立仪器安装到定制的测试系统之中,这通常通过用户或系统集成商实现。比较而言,功能或参数测试仪是一种完全预装 (交钥匙)的系统,其中的大多数硬件和软件集成已经在交付使用之前为用户做好了。这种系统的缺点是成本比较高。开放API系统为用户和系统集成商提供了高度灵活的解决方案,具有实现更低成本的潜力。

图1:基于TSP的多SMU测试系统

采用最新SMU获得更高的吞吐量

测试夹具被加载后,大多数测试时间都是由下列时间段消耗:

1.信号源应用,包括电压或电流瞬态;

2.DUT稳定时间;

3.测量,在需要时变更量程;

4.触发延迟;

5.数据通信;

6.程序执行,包括合格/不合格及装箱决策;

7.测试夹具移动和/或电气切换时间。

通过将独立的仪器转换到集成的SMU测试系统,缩短了独立仪器与PC控制器之间的触发延迟和数据通信时间。一些SMU具备的程序存储器可以运行高达100项的预定义测试,能利用或不用PC进行极限比较、执行条件程序分支等工作。这就减少了较慢的GPIB流量和PC的延迟时间。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)