FloorPlanning 工具是PlanAhead 的一个组成部分,用它可以对FPGA 设计进行分析,首先找到设计中的时序问题或者拥塞的问题,然后再通过使用PloorPlanning 约束,以指导实现工具产生更优的结果。例如,使用LOC 约束可以将Pblock(Phisical Block Region)中的逻辑对象锁定在一个位置或者锁定在一个区域。

为了有效地使用FloorPlanning,必须对Xilinx 的器件结构有较深入的了解,如果不熟悉器件结构,那么通过FloorPlanning 工具生成的布局约束,非但不会提高设计性能,很多情况下还会使系统性能下降。用FloorPlanning 进行布局规划,没有一种现成的、“正确”的规划方案,而是需要经过设计者多次尝试,从而找到合理的规划方案。

1. 指定关键逻辑到Pblock 中。

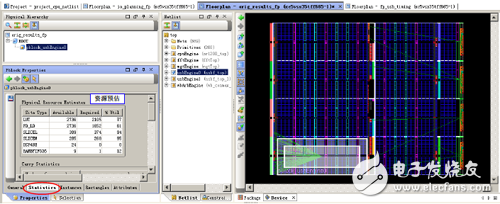

此处我们继续使用10.5 节所用实例,从图10-68 时序分析结果可以看到,此设计有多处时序违例,主要是usbEngine0 和usbEngine1 模块。其实,可以用多种方式使此处时序收敛,我们这里只是介绍一种用FloorPlanning 进行时序收敛的方法。在【Netlist】窗口选择usbEngine0 模块,在其右键菜单中选择【Draw Pblock】,用鼠标左键在【Device】窗口画一个矩形框,并可以通过鼠标拖拉调整矩形框大小,使其可以容纳所有usbEngine0 所需资源。如图10-75 所示。用同样的方法创建usbEngine1 的Pblock。

图10-75 创建Pblock

2. 手动添加LOC 位置约束。

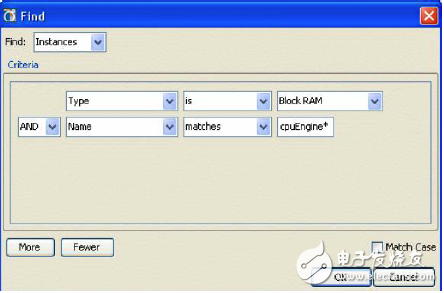

运行Ctrl+F,打开图10-76 查找对话框,按图中所示设置查找条件,单击【OK】开始查找。图10-77 为查找结果。

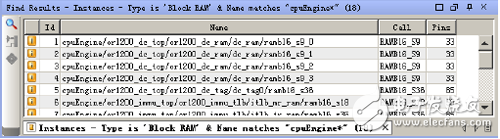

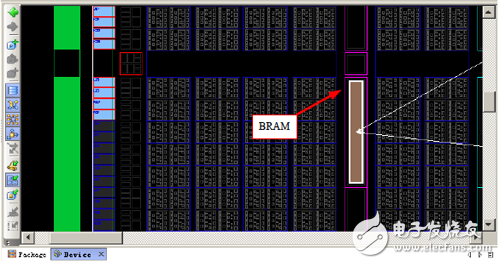

在图10-78 所示的【Device】窗口,单击工具栏的(Create Site Constraint Mode)图标,进入创建位置约束模式。在图10-77 的查找结果窗口选择一个BRAM16,用鼠标拖放到【Device】窗口,找到一个BRAM 资源并释放,这样就为设计中的BRAM16 指定了一个物理位置。

图10-76 查找条件设置

图10-77 查找结果

图10-78 BRAM 位置约束

用这种方法可以指定设计中BUFG、DCM、Port、PPC、MGT 等元素的位置。这里创建的位置约束,是一个固定的约束,会被写入UCF 文件中,它与从ISE 导出的约束有所不同,ISE 导出的约束是不固定的,在【Device】用不同的颜色标识。

建立LOC 约束,除了这里介绍的方法,还可以单击(Create BEL Constraint Mode)按钮,创建基于Slice 的位置约束。

单击(Assign Instance Mode)按钮,创建例化元件的位置约束。

单击【Edit】→【Undo】或者按钮,可以取消位置约束的 *** 作。

3. 查看FloorPlan 的实现结果。

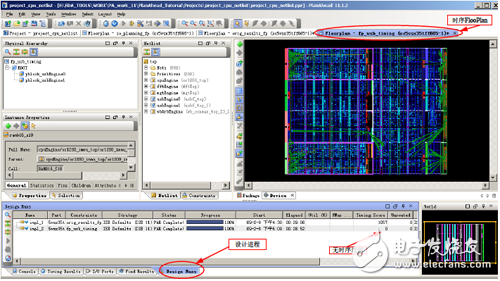

在PlanAhead 主界面,切换到【Floorplan – fp_usb_TIming】视图,如图10-79 所示,单击【Design Runs】标签,可以看到impl_2 的实现结果中TIming Score 为0,说明此实现已满足到时序要求。

图10-79 【Floorplan – fp_usb_TIming】视图

4. 锁定关键逻辑。

FPGA 设计中,逻辑模块的性能经常是不确定的,多次实现结果可能出现较大的差别,为了保证实现的一致性,一个方法就是锁定关键逻辑的位置,例如BRAM 和DSP 资源,这些资源的布局经常会对设计性能产生比较大的影响。我们可以先运行布局布线产生一个满足时序的实现结果,再将这个结果中的BRAM 和DSP 的位置锁定,作为约束指导下次布局布线的参考。

下面介绍锁定BRAM 和DSP 位置。

在PlanAhead 主界面,切换到【Floorplan – fp_usb_TIming】视图,单击【Design Runs】标签,可以看到impl_2实现结果中Timing Score 为0,说明此实现已满足到时序要求,如图10-79 所示,双击打开此实现结果。运行【Edit】→【Find】,按照图10-80 所示设置查找条件,找到设计中所有的BRAM和DSP 资源。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)