Spartan-6 器件最多包含6 个CMT,12 个PLL。PLL 的主要用途是作为频率合成器,产生更宽范围的频率输出,在与CMT 中的DCM 连接时,具有良好的滤波功能。

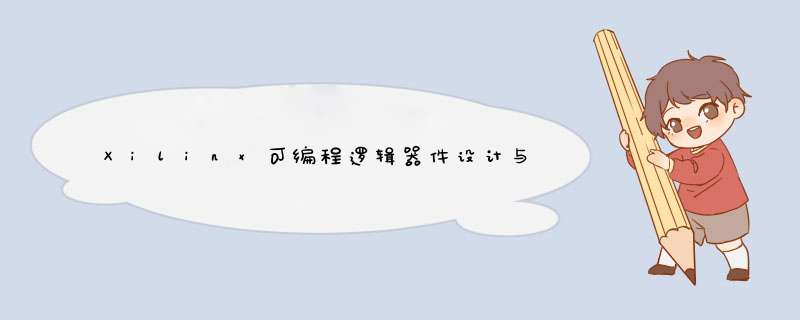

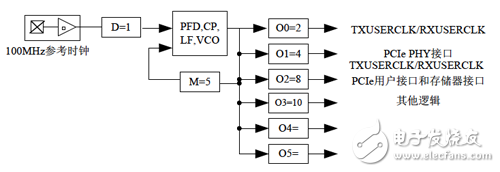

图2-20 Spartan-6 PLL功能框图

其中包括可编程计数器D、相位/频率检测器(Phase-Frequency Detector,PFD)、电荷泵(Charge Pump ,CP ) 、环路滤波器(Loop Filter , LF) 、压控震荡器(Voltage Controlled Oscillator,VCO)、O0~O5 为6 个可编程计数器。

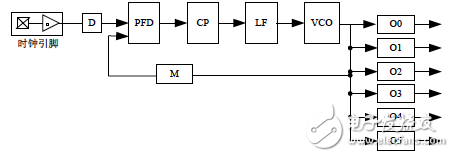

它的工作原理是,PFD将输入时钟与反馈时钟的相位和频率进行比较,产生的信号驱动CP 和LF,CP和LF 为VCO产生一个参考电压,这个参考电压将影响VCO的输出频率。那么VCO的频率是如何变化的呢?PFD完成2个时钟的比较后,产生CP和LF 的驱动信号,这个信号确定了VCO 应该工作在较高频率还是较低频率。当VCO工作频率过高时,PFD触发一个下降信号,致使控制电压下降,从而降低VCO的工作频率。当VCO工作频率过低时,PFD触发一个上升信号,致使电压上升。VCO 共产生8个输出相位,每个输出相位都可选作输出计数器的参考时钟,如图2-20所示。另外PLL 还提供了一个专用计数器M,用来控制PLL的反馈时钟,以实现大范围频率合成。6个“O”计数器可以独立编程,例如,O0可以编程为进行二分频 *** 作,而O1编程为进行三分频 *** 作。唯一的限制是VCO的工作频率对所有输出计数器来说必须相同,因为VCO驱动所有计数器。使用专用PLL 布线资源,必须将CLK_FEEDBACK设置CLKOUT0,按照图2-21所示使用BUFPLL和BUFIO2FB。

图2-21 带CLKOUT0反馈的PLL

当使用CLKOUT0的专用反馈路径时,输出计数器CLKOUT0_DIVIDE将影响VCO频率,fVCO=FIN×M×CLKOUT0_DIVIDE/D。

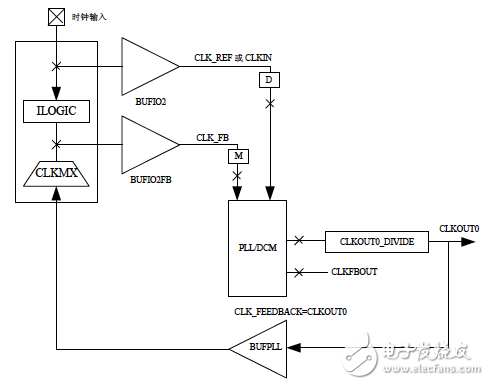

图2-22所示为PLL常用的两个模块,PLL_BASE和PLL_ADV。PLL_BASE允许使用独立的PLL 的最常用功能,包括时钟去歪斜、频率合成、粗粒度相移和占空比编程等。

PLL_ADV具备所有PLL_BASE功能,它具有更多的时钟输出。

图2-22 PLL的原语

Spartan-6 PLL是为支持时钟网络去歪斜SKEW、频率合成和减少抖动而设计的混合信号模块。接下来将详细讨论PLL 的这3种作用。

(1) PLL 对时钟网络去歪斜SKEW。

(2) PLL 用于频率合成。

PLL还可以用于频率合成。在这种应用中,PLL不能用于时钟网络去歪斜,而是用来为其他模块提供时钟。在这种模式下,PLL反馈通路因为要将所有布线保留为局部布线而应设置成internal反馈模式,以尽量减少抖动。图2-23所示为将PLL配置成频率合成器的示例。

图2-23 仅用于频率合成的PLL

在本例中,输入为100MHz参考时钟,设置M=5,D=1,可使VCO晶振的频率为500MHz(100MHz×5),6个PLL输出中的4个编程提供以下时钟。

250MHz GTP收发器时钟TXUSRCLK和RXUSRCLK。

125MHz PCI Express PHY时钟。

62.5MHz PCI Express用户接口和BRAM接口时钟。

50MHz逻辑时钟。

在此示例中,参考时钟和输出时钟之间没有相位关系,但是各输出时钟之间要求有相位关系。

(3) PLL用作抖动滤波器。

PLL始终可以降低参考时钟上固有的抖动。PLL可以被例化以滤掉外部时钟在驱动另一个逻辑模块前(包括DCM)的抖动。作为抖动滤波器,PLL通常被简单地视为一个缓冲器,在其输出上重新生成输入频率(例如,FIN=100MHz,FOUT=100MHz)。通常,将PLL的BANDWIDTH属性设置为Low,可以实现较强的抖动滤波,但要注意,将BANDWIDTH设置为Low会导致PLL的静态偏差增大。

如何使用PLL呢?通常有如下几种方法。

ISE软件中的PLL向导可以帮助生成各种PLL参数。

可以手动将PLL例化成一个组件。

将PLL与IP核合并,IP核将包含并管理PLL。

PLL有5种应用模型,下面分别介绍。

(1) 时钟网络去歪斜。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)