CLB是实现时序电路和组合电路的主要逻辑资源。

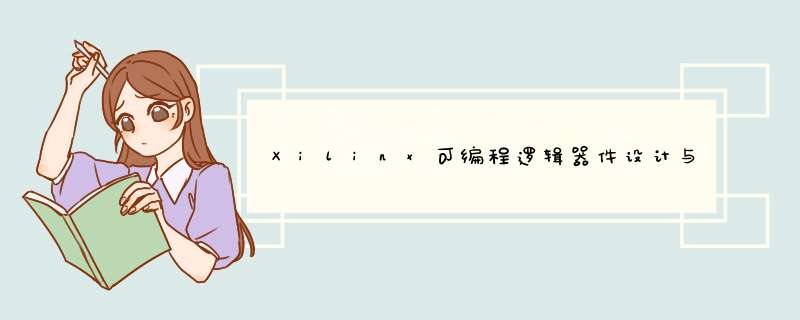

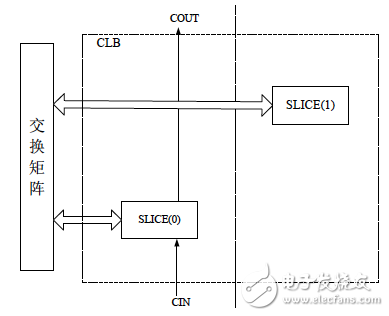

Virtex-6每个CLB模块里包含2个SLICE,每个CLB通过交换矩阵与外部通用逻辑阵列相连,如图5-2和图5-3所示。CLB中的两个SLICE之间没有直接连接。

图5-2 CLB 里的SLICE 排列

图5-3 CLB 的位置排列

在Virtex-6中,SLICE 分为SLICEX、SLICEL 和SLICEM 三种,SLICEX不具有存储功能,也没有进位链;SLICEL不具有存储功能,但包含进位链;SLICEM 具有存储/移位寄存器功能,也包含进位链。

每个SLICE包含4个LUT 和8个存储单元。这些基本单元能提供逻辑、算术和ROM功能。除了这些基本功能,还有一些SLICE具有分布式RAM和移位寄存器功能,这些SLICE又被称为SLICEM。

CLB 可以实现表5-1 所示功能。

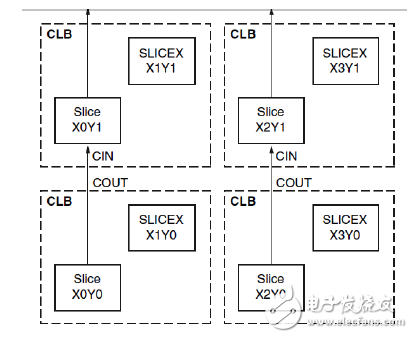

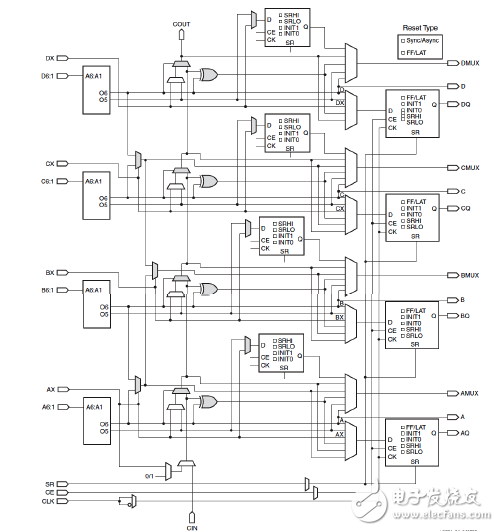

SLICE结构图如图5-4(a)和图5-4(b)所示,每个SLICE包含逻辑函数发生器(即LUT)、存储元件、多功能多路复用器(MUXF)、进位逻辑和算法单元(MULT_AND)等资源。

(a)SLICEM

(b)SLICEL

一、 查找表(LUT)Virtex-6 FPGA的函数发生器由6输入查找表实现。每个LUT有6个独立输入(A1-A6)和2个独立输出(O5 和O6),可以实现任意6 输入布尔函数。同时每个LUT 在相同的输入情况下,也可以实现2 个任意5 输入布尔函数。如果是6 输入函数,仅有O6 输出。

O5 和O6 分别对应两个5 输入函数发生器的输出,在这种情况下,A6 由软件设置为高电平。LUT 的延时与所实现的函数无关。

LUT 可以实现组合逻辑、ROM、分布式RAM、移位寄存器等功能。

(1) 组合逻辑:所有的LUT 可以实现任意6 输入布尔函数。

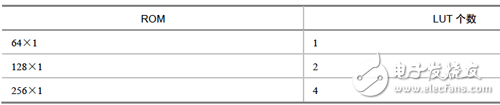

(2) ROM:所有的LUT 可以实现一个64×1 位ROM。有三种配置方式,分别是ROM64×1、ROM128×1 和ROM256×1。SLICEM 和SLICEL 中的ROM 可以级联成更宽或者更深的ROM,配置的表见表5-2。

表5-2 ROM 配置

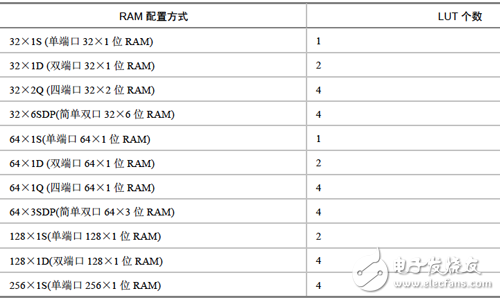

(3) 分布式RAM存储器(只能在SLICEM中使用):SLICEM中的LUT可以配置成一种称为分布式RAM的同步RAM。SLICEM中的多个LUT可以灵活组合起来,以存储更多数据。在SLICEM内可以将RAM元件配置成以下形式,RAM的配置见表5-3。

表5-3 分布式RAM的配置表

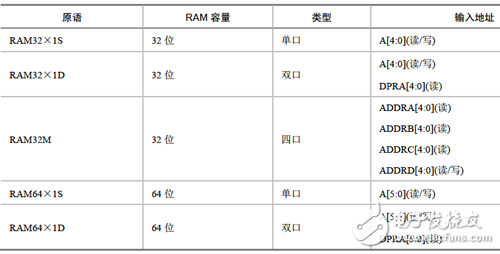

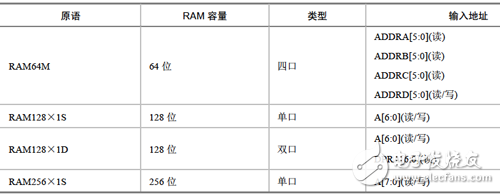

分布式RAM原语如表5-4所示。

表5-4 单口、双口和四口的分布式RAM的原语

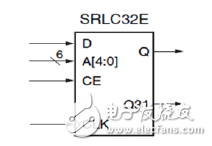

(4) 移位寄存器(只能在SLICEM中使用):SLICEM的LUT还可配置成32位移位寄存器,无需使用SLICE中提供的触发器。以这种方法使用的LUT可以将串行数据延迟1到32个时钟周期之间的任意长度。移位寄存器的移位输入SHIFTIN和移位输出SHITOUT用来将LUT级联成更大的移位寄存器,一个CLB里面的4个LUT可以级联,产生128个时钟周期的延时。CLB之间也可以连接组成移位寄存器,用于平衡数据流水线的时序。移位寄存器原语如图5-5所示。

图5-5 移位寄存器的原语

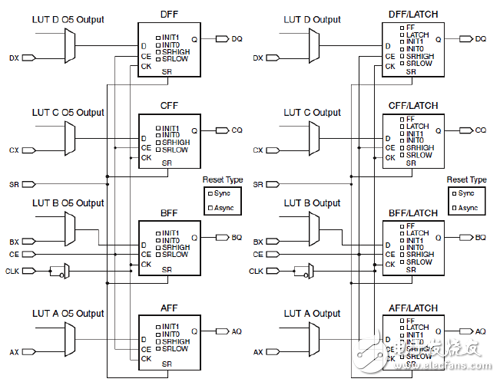

二、 存储元件Virtex-6每个SLICE都有存储元件,可以实现存储功能,可以配置成边沿触发式的D型触发器或电平敏感型的锁存器,如图5-6所示。

图5-6 SLICE里寄存器/锁存器配置

三、 多路复用器(MUX)在一个SLICE中,除了包含LUT外,还包含三个多路复用器(F7AMUX、F7BMUX和F8MUX),用户可以将4个函数发生器组合在一起,构成7输入或者8输入的函数。多于8个输入的函数,可以用多个SLICE实现。

多路复用器F7AMUX、F7BMUX和F8MUX通常和函数发生器或者片上逻辑一起实现多种多路复用器。可以实现以下几种多路复用器。

1个LUT实现4:1多路复用器

2个LUT实现8:1多路复用器

4个LUT实现16:1多路复用器

四、 快速先行进位逻辑(Carry Logic)Virtex-6每个CLB有2条独立的进位链,用于实现快速算术加减运算,它解决了多位宽加法、乘法从最低位向最高位进位的延时问题。先行进位逻辑有专用的进位通路和进位多路复用器(MUXCY),可用来级联函数发生器(LUT),以实现更宽更复杂的逻辑函数,提高CLB模块的处理速度。Virtex6中的进位链是上行进位链,每个SLICE具有4位的高度。考虑到进位链的上行结构特点,在设计中,要特别注意进位链的长度,因为如果当进位链的长度超出一列时,进位链会导致延时变长很多,影响时序。

五、 算术逻辑(MULT_AND)算术逻辑包括一个异或门(XOR)和一个专用与门(MULT_AND),一个异或门可以使一个SLICE实现2位全加 *** 作,专用与门提高乘法器的效率。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)