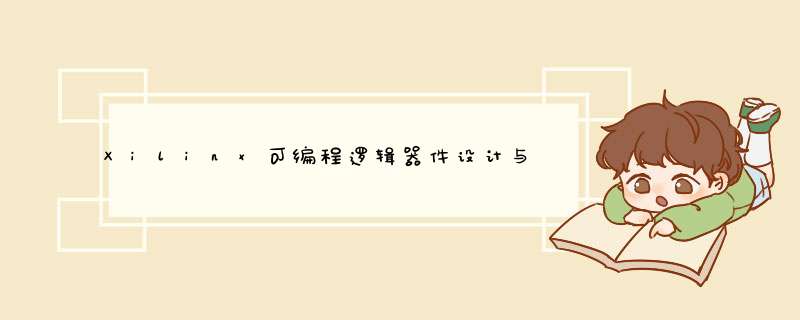

Spartan-6的全局时钟网络由16个位于芯片中央的BUFGMUX驱动。BUFGMUX的输入信号有以下3种。

顶部和底部BANK的时钟输入。

左边和右边BANK的时钟输入。

FPGA内部互联和/或PLL/DCM。

这3种资源通过芯片中央的切换模块切换。

每个BUFGMUX输出驱动一个垂直方向的时钟脊线,沿着这个方向,水平跨接行时钟HCLK。

HCLK的输入有两种,通过专用的多路选择器切换。

BUFGMUX的输出。

PLL或者DCM的输出,每个HCLK对应一个PLL或者两个DCM。

由于Spartan-6中有32个全局时钟输入引脚和16个全局输入缓冲器,所以有可能两个时钟输入引脚驱动一个全局时钟。当通过全局时钟引脚(IBUFG或IFUFGDS)直接驱动全局时钟缓冲器(BUFG或BUFGMUX)时,BANK0、BANK1和BANK5分享8个全局时钟缓冲器,类似地,BANK2、BANK3和BANK4分享8个全局时钟缓冲器,如图2-14所示。

图2-14 Spartan-6 FPGA全局时钟结构图

为了增加布线的灵活性,当使用第二个BUFIO2时,BUFIO2可用作第二个全局时钟缓冲器。由于系统资源按照主BUFIO2路径优化,因此对于不使用主BUFIO2资源的全局时钟,系统性能会受影响。

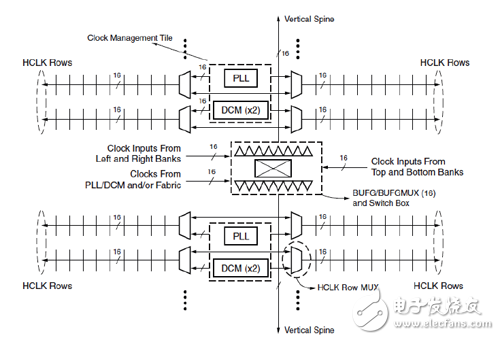

(2) I/O区域时钟网络。如图2-15所示,一个I/O时钟网络能通过BUFPLL被PLL驱动,每个PLL有2个相关缓冲器,扩展到整个I/O BANK。

图2-15 Spartan-6 FPGA I/O BANK内的I/O时钟结构

每个BANK有两个分离的I/O时钟区域,每半个I/O Bank都有4个高速I/O时钟,由4个专用BUFIO2缓冲器驱动。

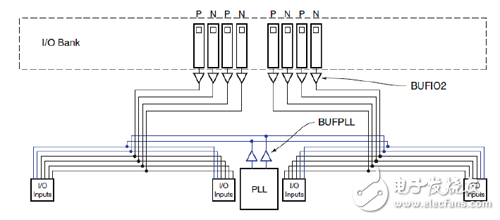

I/O时钟输入引脚可以通过BUFIO2扩展到整个BANK,如图2-16所示。使用两个BUFIO2资源,例如BUFIO2_0和BUFIO2_4,将时钟扩展到整个BANK。

图2-16 I/O BANK内的I/O时钟

当输入延时使能的时候,一个输入引脚不可以驱动两个BUFIO2缓冲器。BUFIO2除了提供输入引脚到I/O时钟网络上,还提供了到PLL/DCM和BUFG的专用时钟路径。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)