多年以来,多少厂商前赴后继,试图让FPGA开发更简单,但是他们都成了FPGA历史长河中的一抹红晕。

今年以来,FPGA在产业的关注度迅速提升,一个原因是其与人工智能、VR等热门应用密切相关,另个原因是国际大厂如英特尔以及本土巨头如紫光集团等对FPGA的青眼有加, 收购融资热门不断, 大有与CPU, GPU分争天下的趋势。 然而, 传统上FPGA开发绝对不像X86处理器那样简单,需要专业的工具以及专业的知识甚至芯片设计基础,开发其应用主要途径是采用最底层的硬件实现,这也是阻碍其普及一个因素。

一方面FPGA成为势不可挡的趋势, 一方面其用户局限在少数硬件工程师手中。如何解放FPGA,让更多的应用能够获益于FPGA的灵活、高性能功耗比的优势呢? 这个问题, 在过去的几年中, 从来不乏各种各样的尝试, 试图降低FPGA的开发门槛,而大多数最终都成为无足轻重的历史。最终能够改变这个历史的, 恐怕还得靠赛灵思这个龙头老大。 除了推出软件定义的设计环境如SDSoC,SDAccel, SDNet让软件工程师可以轻松开发FPGA应用之外,其通过支持和打造一个生态合作伙伴环境,正在解放FPGA现有局限。 最近, 其合作伙伴PLDA开发出一种新流程, 有望让FPGA实现真正的大众化。

PLDA所开发出的一种称作 QuickPlay 的工作流程,号称可以高效解决实现复杂性问题,为 FPGA 开发提供多种使用模式。其价值核心是其软件开发人员将原本用于 CPU 的应用,部分或全部地实现在 FPGA硬件上。QuickPlay 能够全面发挥 FPGA 资源的作用,将这些功能强大而复杂的器件转化为软件定义平台,无需艰苦的硬件设计即能获得 FPGA 带来的优势。牛吧!

做过设计的人都知道,硬件执行算法无论是时间还是功耗上都占有极大的优势,用DSP软件去做图像处理不仅耗时且功耗极高,而用FPGA来做,效率则高得惊人!

QuickPlay是什么样的流程?

任何旨在使用自定义硬件帮助软件开发人员来增强其应用的工具应该有如下特点:

从纯软件代码中创建功能硬件;

根据需要采用现有的硬件 IP 模块;

调用并创建所有的支持硬件(接口、控制、时钟等);

支持使用现成商用开发板以及自定义平台;

确保生成的硬件能自动建构校正,这样无需进硬件调试;且

支持仅使用标准软件调试工具即可调试功能模块。

PLDA 设计 的QuickPlay 以满足所有各项要求,让纯软件开发人员以极小工作量就能指定、构建和集成 FPGA 到自己的软件架构中。

以软件为中心的方法

使用 QuickPlay 实现整个设计流程相当简单直观:

1. 开发硬件引擎的 C++/C++ 语言功能模型。

2. 使用标准的 C/C++ 语言调试工具来验证功能模型。

4. 编译并构建硬件引擎。

QuickPlay 使用直观的数据流模型,能从数学角度保证可确定性执行,与执行引擎无关。该模型由称之为内核的并行功能组成,负责与流通道进行通信。因此它与软件开发人员在白板上勾勒应用草图关联紧密。为确保行为的确定性,这些内核必须彼此进行通信,以防发生竞态条件和死锁等数据冲突。实现这一要求的方法是使用具备下列特点的流通道:(1)基于 FIFO,(2)阻塞式读取和阻塞式写入,以及(3)点对点。

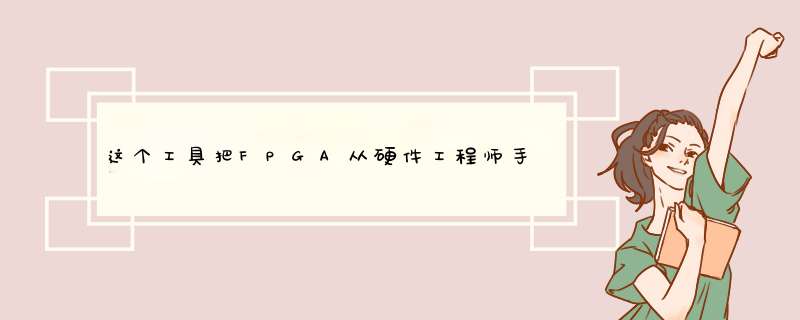

这些就是 PLDA 据以构建 QuickPlay 的计算模型—— 卡恩进程网络(KPN)的特点。图 1的QuickPlay 设计实例描述了 KPN 模型。

图1 — QuickPlay 中的设计实例

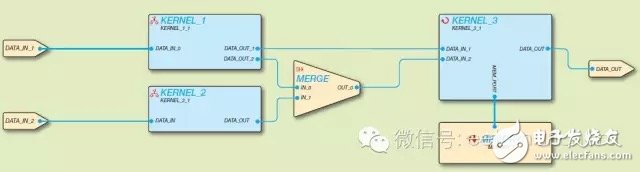

任何内核的内容都可以是任意 C/C++ 语言代码、第三方 IP,甚至是 HDL 代码(对硬件设计人员而言)。QuickPlay 采用相当简单直观的设计流程(图 3)。

图 2 — QuickPlay 采用简单直观的设计流。

QuickPlay 带给开发者的好处是什么?QuickPlay带来的好处很明显,开发者再不用关心内核功能发生了什么,也不用担心硬件工程师经常遭遇的的时序、时钟、通信堆栈、协议以及其他类似问题了,只要约束得到,也不用做硬件级的验证和调试。这是真正让软件开发者可以轻松开发FPGA的好工具。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)