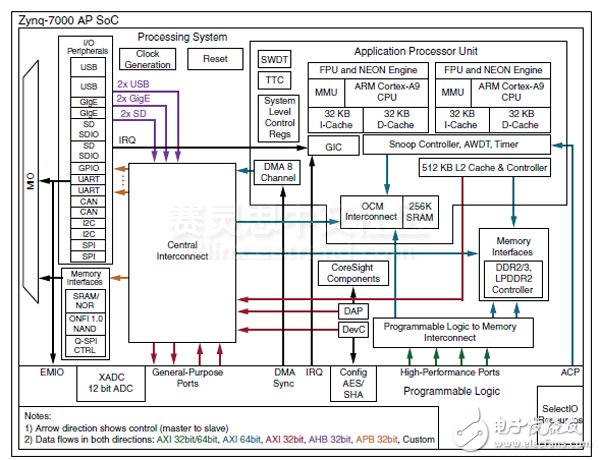

到目前为止我们摸索使用过的Zynq All Programmable SoC PS(处理器系统)部分的所有设备都是只利用了一个ARM Cortex-A9处理器内核(内核0),然而在Zynq SoC 的PS部分包含有两个处理器内核,对于很多应用程序来说我们想要利用两个处理器内核,这样才能取得最大化的性能。使用两个处理器内核处理不同的任务被称作非对称多处理机制(AMP),而且包含不同的组合方式:

在内核0与内核1上运行不同的 *** 作系统

在内核0上运行 *** 作系统,在内核1上执行程序代码(或者反过来)

在两个处理器内核上执行不同的程序代码

有两种多核处理的方法:对称机制和非对称机制。在我们介绍这两种方法的区别前,我们要先清楚什么是多核处理:

“多核处理是在一个系统中采用不止一个处理器内核。这可以实现同时完成多条指令的执行,然而这并不一定是必须的。”

多核处理的对称机制与非对称机制的区别如下:

对称的多核处理是当运行很多个软件任务时会将处理器负荷分配到多个处理器内核上。

非对称的多核处理机制是利用专用的处理器执行专用的应用程序或者在完全相同的处理器上执行专门的应用程序。

在接下来的及篇博客中我们将会摸索介绍Zynq SoC上的非对称多核处理机制(AMP)。但是现在我们要先了解两个应用程序代码,这两个应用程序会在不同的处理器内核上运行。

当我们要在Zynq SoC上采用非对称的多核处理机制(AMP),我们必须考虑到Zynq SoC上的两个处理器内核都有各自独占的资源,同时它们也共享一些资源。这两个处理器内核都有各自的L1指令和数据缓存、定时计数器和使用共同中断控制器的看门狗(它们有公用的中断号和自己专用的中断号)。然而Zynq SoC上的中断并不是非常简单明确的,因为PS部分的每个内核能都利用软件中断实现对自己本身、另外一个处理器内核或者同时两个处理器内核的中断,软件中断机制是通过借助中断控制器实现的。

我们想要利用DDR存储器来运行这两个处理器内核,那我们必须清楚了解每个处理器内核的内存映射地址范围。地址信息是由每个应用程序的连接脚本决定的。如果我们不清楚这些映射地址信息,当应用程序在不同的内核上执行时就会干扰其他的应用程序的 *** 作,就会出现各种错误信息,也就是我们常见到的Bug。

我们同时也要修改由SDK自动生成的文件信息 来使系统启动并运行起来。第一步是使用XAPP1079脚本修改第一阶段启动加载文件,这个脚本检查了应用程序代码和AMP设置代码。

我的打算是先创建一个简单的系统以便系统启动和运行起来后,我们可以进行一些扩展 *** 作。第一个应用程序是使用Zynq SoC的处理器内核0通过RS232通信协议与用户实现实时通信,内核1执行的 *** 作是控制MicroZed I/O扩展板卡上的LED灯,这两个程序的执行将不会出现互相的干扰。

接下来我们将探索怎样利用片上存储单元(OCM)建立处理器之间的通信通道,以及我们怎样共享两个处理器之间的资源。最后我们将会探索研究同时在两个处理器上运行的程序代码,研究怎样在一个或者两个处理器内核上运行 *** 作系统。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)