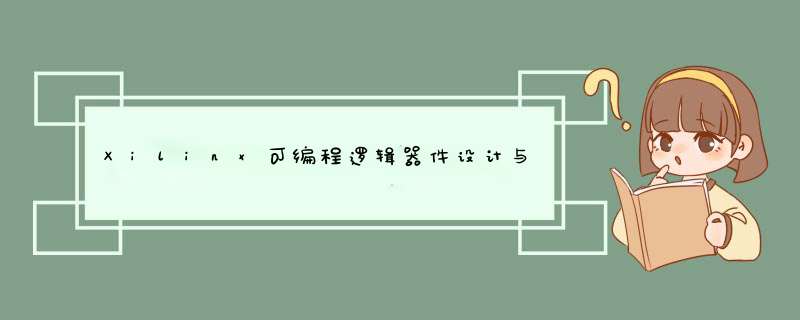

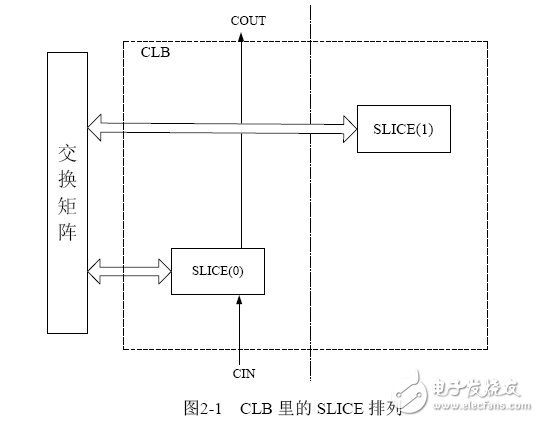

Spartan-6每个CLB模块里包含两个SLICE。CLB通过交换矩阵和外部通用逻辑阵列相连,如图2-1和图2-2所示。底部的SLICE标号为SLICE0,顶部的SLICE标号为SLICE1。两个SLICE没有直接连接。

在Spartan-6中,大约50%的SLICE为SLICEX,它不具有存储功能,也没有进位链;25%为SLICEL,它也不具有存储功能,但包含进位链;剩下的25%为SLICEM,它具有存储/移位寄存器功能,也包含进位链。注意XC6SLX4不含SLICEL。

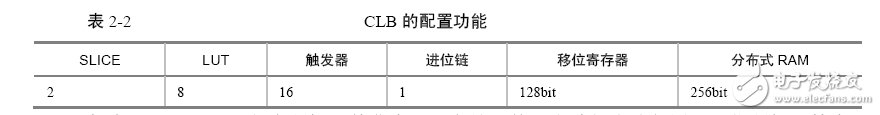

所有CLB的功能是相同的,能够完成表2-2中的配置。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)