在我的上一篇文章中,我讨论了 (ADC) 的2个重要特点。这2个特点简化了抗混叠滤波器的设计:一个过采样架构和一个补充数字抽取滤波器。这个过采样架构将那奎斯特频率放置在远离信号带宽的位置上,而数字抽取滤波器衰减大多数有害的带外信号。当把二者组合在一起时,它们可以实现更加自由的抗混叠滤波器响应,只需几个分立式组件即可实现这一功能。

图1:用一个适当的抗混叠滤波器来阻止这些混叠

我们知道,在高精度ADC应用中使用抗混叠滤波器是有益的,不过,设计合适的抗混叠滤波器也同样重要—如果你不小心的话,就像把有害误差从系统中消除一样,很容易将有害误差引入到你的系统中。在为你的应用设计抗混叠滤波器时,请考虑以下3个通用指导原则:

选择你的滤波器截止频率

最简单的抗混叠滤波器是一个单极、低通滤波器,如图2所示,它使用一个串联电阻器 (R) 和共模电容器 (CCM)。设计这个滤波器的第一步就是选择所需的截止频率,fC。在fC上,滤波器的响应滚降至-3dB,并且在频率域范围内继续以-20dB/十倍频的速度减少。

选择一个比ADC调制器采样频率,fMOD,至少低十倍频的截止频率,其目的在于,在这些频率上以10倍或更高倍数打压带外噪声。对于增加的衰减,通过增加R和CCM 的值来进一步减少截止频率。我在上一篇文章中提到过,你的数字抽取滤波器的用途就是提供帮助,所以就没有必要在所需信号带宽之后立即设定你的抗混叠滤波器截止频率。

方程式1计算出单极、低通滤波器的截止频率为-3dB:

图2.ADC输入上的单极、低通滤波器

有时候,一个单极、低通滤波器也许还不够。诸如振动感测等应用也许是用更少的过采样来分析更宽带宽上的信号。这就使数字抽取滤波器的通带更加靠近fMOD,并且使得抗混叠滤波器的滚降空间更小。在这些情况下,你可以添加一个包含额外RC对的第二极或第三极,以实现一个更加灵敏的滤波器响应。

图3中显示的是,设计用于ADC的单极和双极滤波器的响应;这个ADC在fMOD = 1MHz上对输入进行采样。双极滤波器扁平通带向外扩展至大约20kHz,并且仍然能够在1MHz上实现-60dB的衰减。

图3.单极和双极低通滤波器的频率响应

考虑差分与共模滤波器之间的关系

很多ADC转换两个独立输入之间(例如INP与INN)的电压,所以,设计人员经常在每个输入上放一个共模滤波器,以保持系统共模抑制 (CMR)。然而,组件容差将使任意两个滤波器不匹配,并且会降低频率范围内的CMR性能,这是因为对共同信号的滤波 *** 作不同。这就通过人们已知的共模至差分转换产生一个差分信号误差。

方程式2使用电阻器容差,RTOL,和电容器容差,CTOL,计算出共模抗混叠滤波器在指定频率下的CMR:

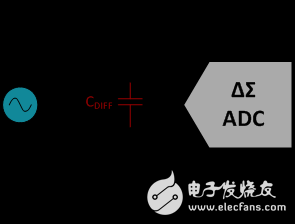

对于需要高CMR的应用,如图4中所示,可以考虑添加一个差分滤波器,以便为2个共模滤波器提供补充。通过将差分电容器CDIFF 增加到比CCM大10倍,将差分截止频率设定为比共模截止频率低10倍频。这样可以减轻由共模组件不匹配所引入的误差,并且生成一个更加灵敏的总体滤波器响应。方程式3计算出差分低通滤波器的截止频率。需要注意的是,分母中有一个额外的因子2。

图4.添加了一个差分滤波器的共模滤波器

3.选择合适的组件值

将电阻器添加到信号路径中将在测量中引入有害噪声和误差,所以,不论何时都有必要将它们控制在合理的范围内。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)