近年来,高精度Σ-∆ 模数转换器成为集成电路设计的研究热点,其应用领域包括:电机电枢电流测量、通用电流测量、精密转换测量、工 业过程控制、重量测量、印刷和便携仪器、压力传感器测量等。Σ-∆ ADC前端的调制器利用过采样的方法将量化噪声搬移到高频段,后端的数字抽取滤波器必须再将高频噪声滤除,所以数字抽取滤波器的性能在整个Σ-∆ ADC中起着非常重要的作用。我们选用了一种抽取滤波器Sinck数字滤波器,它可以有效的滤除高频噪声满足设计的需要,并且这种滤波器的算法中不需要乘法。

Σ-∆调制器的时钟频率 、抽取率M和输出速率 三者之间的关系为

Sinc滤波器阶数k的选择必须先知道滤波器前端 调制器的阶数,Sinc滤波器的阶数至少要比Σ-∆调制器的阶数大于1,必须满足

Sinc滤波器输出数据的位数、滤波器的阶数k和抽取率M三者之间满足

因为滤波器内部有累加器,所以经过多级累加器之后,内部总线位数就会比输出数据的位数宽。又由于在滤波器内部有累加器也有差分器,所以内部总线的位数需要大于输出数据位数1位。

Sinc滤波器在抽取数据滤波的同时也会产生直流增益GainDC=Mk。

2 Sinc3 Filter设计与实现虽然Sinc3滤波器算法中没有复杂的乘除,但是滤波要求处理速度较快,需要达到10MHz或者更高,对于采样频率高的Σ-∆调制器要求滤波的速度就更快了。本文利用Xilinx的Spartan-3E系列的XS3S500E-FG320实现该设计。

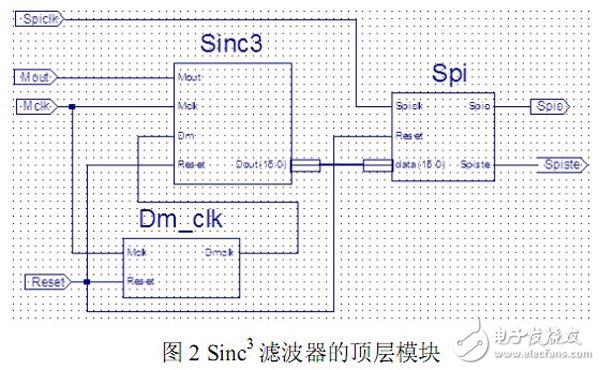

图2所示为Sinc3滤波器的顶层模块。本设计顶层模块利用原理图输入的方式,各个底层模块采用Verilog HDL语言编写。顶层模块包含三个子模块分为:抽取时钟信号发生模块、Sinc3滤波模块及与DSP进行串行通信的模块。每一个模块单独完成一个功能,由Σ-∆调制器产生的Mout、Mclk(Mclk的频率为Σ-∆调制器的采样频率)信号作为滤波器的信号输入,经过Sinc3滤波模块后,输出一个并行数据,对于不同抽取率可以根据式(4)计算出输出并行数据的位数。抽取时钟信号DMclk的频率由抽取率M和Mclk决定,大小为Mclk频率的M次分频。 Spio、Spiclk和Spiste是FPGA与DSP进行SPI通信的接口,Spi模块的作用是将Sinc3滤波模块输出的并行数据转换为SPI的通信模式与DSP通信,将采集的模拟量数据送入DSP进行处理。Reset信号是AD采样的同步信号,保证所有模块在每一个采样周期开始时都进行初始化。

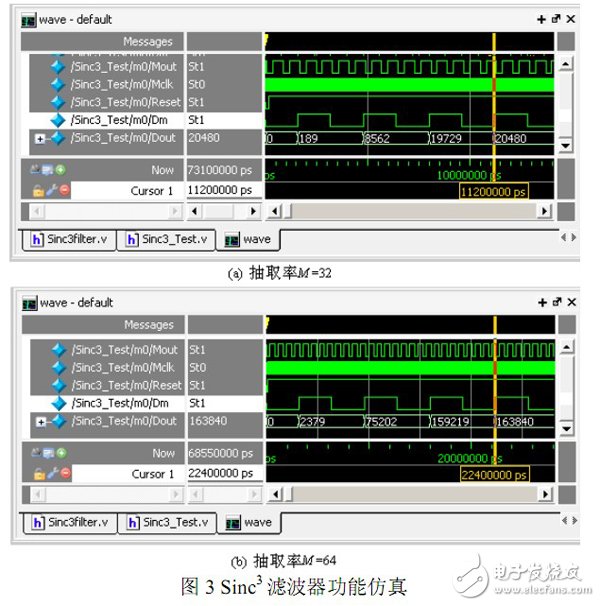

完成系统的功能设计和输入后,利用Modelsim SE软件对Sinc3滤波模块做了功能仿真。在仿真测试文件中产生一个时钟激励信号模拟Mclk信号,同时产生一个和Mclk信号对应占空比可调的激励信号模拟Mout信号,模拟Σ-∆调制器测量恒定模拟量时产生的信号。将Mclk信号的频率设定为10MHz,并把Mout信号的占空比定为5/8,周期定为800ns。编写好测试文件后,将测试文件添加到所设计模块的工程文件中,利用编写好的测试文件分别对抽取率为32和64的Sinc3滤波器进行测试分析,仿真输出信号波形如图3所示。由前文可知32和64时对应的直流增益分别为32768和262144,滤波器的输出结果Dout分别为20480和163840,比上滤波器对应的直流增益都等于5/8,与Mout信号的占空比相等,因此所设计的滤波器在功能上满足滤波要求。比较(a)和(b)两图可以发现抽取率变大时,抽取的采样点数增多,滤波器的直流增益增大,这样可以更准确的还原采样结果,但是会导致采样滤波的响应时间变长,输出数据速率降低。因此滤波器抽取率的选择需要根据实际情况决定,合理选取抽取率。

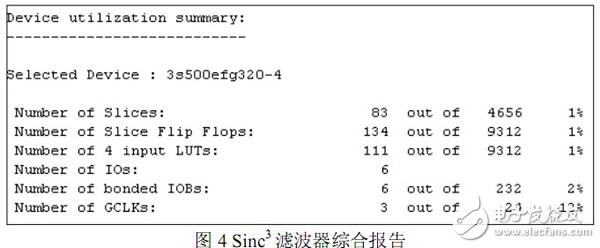

功能仿真验证结束,对系统综合,加载约束条件,成功综合后得到综合信息报告如图4所示。实验中只设计了一路滤波器,从综合信息报告中可以看出消耗资源较少。在实际应用中一片FPGA可以设计多路滤波器,如果采用的Σ-∆调制器的阶数较高,需要的滤波器的阶数也就越高,滤波器阶数升高后消耗FPGA的资源会成倍的增加。

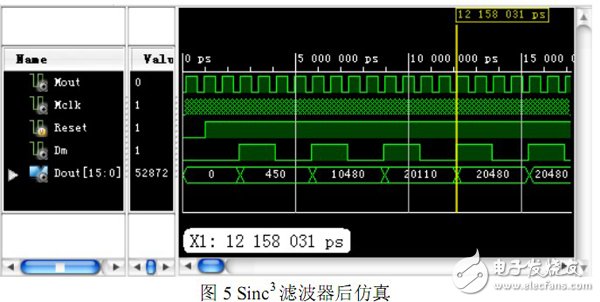

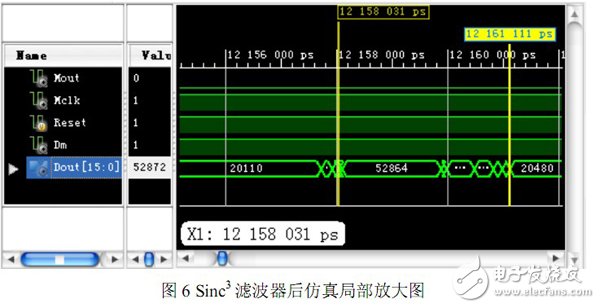

为了估计门延时给系统带来的影响,利用ISim对系统做了综合后仿真。仿真波形如图5所示。可以看出,加入延时文件后,输出结果变化时,在抽取时钟的边沿处产生毛刺,出现了错误的数据。图中的标线处输出结果Dout中出现了52872错误的数据。将仿真波形局部放大如图6所示,从图中可以看出在边沿处出现的毛刺持续时间都很短,所有毛刺数据持续时间都小于3ns,对于这样短暂的毛刺信号,在FPGA内部是无法捕捉到的,因此产生的这些毛刺信号不会对最终的输出结果产生影响,所以后仿真实验结果证明所设计的系统可以正常工作。

仿真结束,生成下载文件下载到芯片内,通过调试验证,实验结果正确,符合设计要求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)