基于FPGA的无线通信收发模块设计方案

1 前言

近年来,随着半导体工艺技术和设计方法的迅速发展,系统级芯片SOC的设计得以高速发展,这已成为业界热点。但是,由于SOC产品设计具有开发周期相对较长、高成本和高风险等特点,对市场的变化非常敏感,这使得SOC在消费电子、汽车电子、工业设计领域的发展进程仍然缓慢。与此同时,当今的制造工艺能够提供更多更高速的逻辑、更快的1/O和更低价位的新一代可编程逻辑器件,现场可编程门阵列(FPGA)己然进入嵌入式应用领域,高性能FPGA也不再局限于引进系统粘合逻辑,也可作为SOC平台,而在过去,由于性能缘故,只有专用集成电路(ASIC)或专用标准产品(ASSP)才能达到相应的要求。不仅如此,由于FPGA的现场可编程特征,它己成为更具灵活性和广泛性发展前景的工业设计平台。

FPGA可轻易地被修改变更、修复缺陷,或在用户需要升级和配合市场发展时去创制未来的衍生产品。这一趋势在工业无线通信设计方面更加明显。当考虑到上市时间、实施灵活性及未来过时等问题时,采用FPGA作为专用芯片设计是一个最佳的项目实施方案。

基于摩尔斯信号的通信是人类最早的无线通信方式,它仍应用在海事移动通信、航空移动通信、广播、卫星通信当中。由于摩尔斯电码信号通信的传统性、经济性和有效性,它在海事移动通信中仍占主导地位,特别是船与船、船与岸、岸与船之间的摩尔斯通信更是占据通信业务总量的80%以上。

基于PC机的MORSE电码信号自动处理己经实现,但在海事移动通信中,它还是受到一些客观条件的约束,缺泛方便性和灵活性。本文从基于FPGA平台的专用芯片设计技术入手,分析和设计了一种摩尔斯电码的无线通信发射模块设计方案,并对设计进行了仿真验证。

2 可编程逻辑电路设计方法

基于可编程逻辑电路的设计基本方法,一种是传统的系统硬件电路设计方法,它是采用自下而上(bottom-up)的设计方法。另一种就是20世纪80年代开始兴起的EDA(Electronic Design AutomaTIon)硬件电路设计方法。

随着大规模专用集成电路的开发和研制,为了提高开发效率和增加己有开发成果的可继承性,以及缩短开发时间,各种新兴的EDA工具开始出现,特别是硬件描述语言HDL(Hardware DescripTIon Language)的出现,使得传统的硬件电路设计方法发生了巨大的变革,新兴的EDA设计方法采用了自上而下(top-down) 的设计方法。所谓自上而下的设计方法就是从系统总体要求出发,自上而下地逐步将设计内容细化,最后完成系统硬件的整体设计。利用语言对系统硬件电路的自上而下设计一般分为三个层次:第一个层次为行为描述,它是对整个系统的数学模型的描述;第二层次是寄存器传输描述RTL,又称为数据流描述; 第三层是逻辑综合。

利用逻辑综合工具,可将RTL方式描述的程序转换成为用基本逻辑元件表示的文件一门级网表,也可将综合结果以逻辑原理图方式输出,也就是说逻辑综合结果相当于在人工设计硬件电路时,根据系统要求画出了系统的逻辑电原理图。再对逻辑综合结果在门电路级上进行仿真,并检查定时关系,如果一切正常,那么系统的硬件设计基本结束。自上而下设计系统硬件的过程如图一所示。

图一:自上而下设计系统硬件的过程

由逻辑综合工具产生门级网表后,在最终完成硬件设计时,还可以有两种选择:一种是由自动布线程序将网表转换成相应的ASIC芯片的制造工艺,定制ASIC芯片;第二种是将网表转换成相应的PLD编程码点,利用PLD器件完成硬件电路的设计。

3 基于FPGA的摩尔斯码功能结构设计

摩尔斯电码被视为一种开关键控的数据模式,摩尔斯电码中的‘划’比‘点’的时间长3~4倍,不同的‘点’和‘划’组合形成长短不一的摩尔斯电码,不同的摩尔斯电码表示不同的电报符号。发信者先将所要传递的文字翻译成电报符号,再利用电报机发送出去,收信者将收到的电报符号翻译成报文,以此实现无线文字的传播。目前通过微机模拟的方法实现摩尔斯码信号的自动处理,使无线摩尔斯码信号数据进入计算机信息网的方案已得到解决,利用微机处理摩尔斯的方案是先通过软件编程的方法将ASCLL码进行摩尔斯编码,然后通过微机并口发送摩尔斯电码信号,接收时,先通过声频卡来识别接收摩尔斯电码信号,最后通过软件解码成ASCLL码,此方法在成本相对较高,在实际应用中缺乏方便性和灵活性。

根据海洋通信业务的要求,MORSE码处理系统功能定义为:其一、根据指令自动编码、串行发送MORSE码。即根据指令可自动提取ASCLL码,再将ASCLL码自动编码成摩尔斯编码,将编好的MORSE码自动串行发送输出。其二、根据指令自动接收、解码摩尔斯码,并将ASCLL码送入系统。即根据指令自动接收摩尔斯码输入,将接收的摩尔斯码自动解码成ASCLL码。将ASCLL码存储至目标地址或送入系统处理。

通过对摩尔斯码特点的研究可知,在设计摩尔斯码收发模块中必须要有能接收和发送摩尔斯码信息帧的串行异步通信模块。首先,该串行通信模块在指令的控制下,要具有摩尔斯码的自动发送能力,同时具有MORSE码的识别接收能力,因为摩尔斯码串行异步帧的起始位和停止位都不同于ASCLL码串行异步帧,并且不同的摩尔斯码串行帧长度也不一样。二是摩尔斯码的解码和编码问题,因为计算机内核是以ASCLL码为信息交换码的。

由此而来,只要设计出具有接收和发送MORSE码串行信息帧功能,并且具有解码和编码摩尔斯码功能的串行通信子模块,并将其嵌入在系统总线上,则用计算机直接处理MORSE码就成为可能。据此分析,可以得出摩尔斯码收发模块的设计要求,一方面能从串行接收端将摩尔斯码解码成并行的ASCLL码,另一方面能将并行的ASCLL码编码成串行摩尔斯码。由此,本文设计的基于FPGA的摩尔斯码收发模块内部组成框图如图二所示。

图 二:基于FPGA的摩尔斯码收发模块内部组成框图

该处理系统的主要功能模块有:

- 核心控制模块

- 总线控制模块

- 可编程中断处理模块

- 可编程串行接口单元(SIU)

- 可编程定时计数器0~3(TImer0~TImer3)

- 可编程摩尔斯码异步收发模块

中断处理模块有4个外中断源(int0~int3)和6个内中断源(TF0~TF3、T1/R1、mT1/mR1),SIU是系统的通用串行接口,它有4种工作模式,工作模式1~3是通用串行异步接收发送USART(Universal Serial Asynchronous Receiver/Transmitter)工作方式。当SIU工作于工作模式1或3时,Timer1是其波特率发生器。

4 仿真与验证

设计的验证包括功能仿真、时序仿真和电路验证。仿真验证往往是借助第3方提供的EDA开发工具软件包或专用仿真工具软件来实现的。电路验证还需要开发验证平台,对于系统级芯片验证平台的设计也是一项艰巨而不能回避的任务。

本文选用的是Altera公司的MaxPlusII作EDA开发工具,MaxPlusII编译器支持功能仿真(前仿真)和时序仿真(后仿真)。完成源代码(VHDL)设计输入之后,若要进行功能仿真,则在MaxplusII/Compile下,通过选择Processing菜单下的Functional SNF Extractor命令,打开功能仿真器网表文件(SNF)提取器,再进行编译仿真;若要进行定时模拟(时序)仿真,则须在MaxPlusII/Compile下,选择Processing菜单中的Timing SNF Extractor命令,打开定时模拟器网表文件提取器来进行编译仿真。

电路验证就是器件编程测试过程。对于常规的芯片设计,时序仿真结束后,仿真软件就可以产生供器件编程使用的数据文件。对EPLD/CPLD来说,是产生熔丝图文件,即JED文件,对于FPGA来说,是产生位流数据文件(Bitstream Generation),然后将编程数据下载到对应的具体可编程器件中去,然后对其进行实际环境的电路测试。

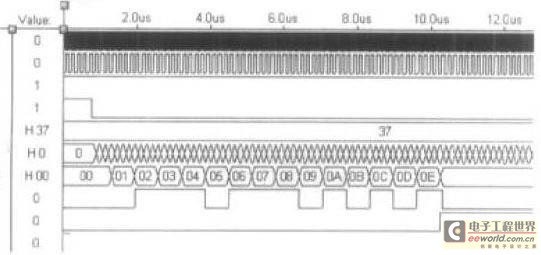

本文选择CLK频率为25MHZ,波特率为25M/16=1562500bps。当发送字符‘7’,执行发送命令后,将启动数据发送的进程,将字符‘7’的ASCLL码值送入ASCLL码发送缓存器,通过MaxPlusII的Simulator仿真器,进行时序仿真验证,研究结果如图三所示。从图中可看出,串行信号端子输出的“2长划”,“3点”,经查表对应的就是摩尔斯数字‘7’,证明数据发送是正确的。另外当数据输出结束后,立刻置高电平,即产生中断信号mTI,字符‘7’的发送用时大约10us。

图 三:仿真验证数据

5 创新点总结

本文的创新点在于提出了一种基于FPGA的无线通信收发模块,并以当今海事通信中占重要地位的摩尔斯电码为例,研究了摩尔斯电码的数字化编码方法,并通过大量的分析设计和实验仿真,实现了基于FPGA处理摩尔斯电码的收发模块,仿真结果也验证了本文所设计的摩尔斯电码数字化编码方法正确可行,工作运行可靠。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)