本文主要介绍利用FPGA的自身的特性实现随机数发生器,在Virtex-II Pro开发板上用ChipScope观察随机数序列,以及在PCIe4Base(基于Virtex-4 FPGA)上实现。

基本的原理

随机数在计算机科学中的密码学中有着重要的用途,常常被用作密钥的来源。随机数包括伪随机数以及真随机数。伪随机数是通过一定的算法计算得出,具有类似于随机数的统计特征,这样的发生器称为伪随机数发生器。而真随机数是通过物理现象产生,例如使用电子元件的噪声、核裂变等等作为噪声源[2],这样的随机数发生器叫做物理随机数发生器,也叫做真随机数发生器(TRNG:Ture Random Number Generator)。

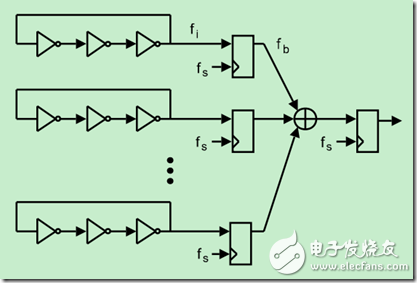

基于FPGA的随机数发生器基本原理是利用奇数个反相器组成振荡器作为随机数发生器的噪声源,因为由于FPGA自身的特性--信号传输存在抖动,所以多个反相器组成振荡器输出也不是很稳定的时钟信号,每个振荡器输出不是相同的,这样成为了理想的噪声源,见图1。振荡器输出通过D触发器进行采样输出,采样频率是fs,然后多个采样输出结果经过异或门之后再通过一个D触发器进行采样,采样频率还是fs。这样简单的随机数发生器就完成了。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)