电路功能与优势

该电路是灵活的频率捷变中频至基带接收机。中频和基带上的可变增益用于调整信号电平。 ADRF6510 基带ADC驱动器还包括可编程低通滤波器,可消除通道外阻塞和噪声。

此滤波器的带宽可随着输入信号带宽变化而动态地调节。这样可以确保由本电路驱动的ADC的可用动态范围得到充分使用。

电路内核是IQ解调器。 ADL5387 基于2×LO的相位分离架构支持宽频率范围工作。精确的正交平衡和低输出直流失调确保了对误差矢量幅度(EVM)的影响极小。

本电路内所有元件间的接口均采用全差分式。如果不同级间需要直流耦合,相邻级的偏置电平彼此兼容。

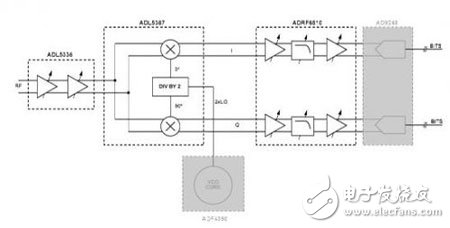

图1. 直接变频接收机原理示意图(所有连接和去耦均未显示)

电路描述

接收机架构

本电路笔记中描述了接收机的直接变频(也称为零差或零中频)架构。与可以执行多次频率转换的超外差式接收机相比,直接变频无线电只能执行一次频率转换。一次频率转换的优势如下:

降低接收机复杂性,减少所需级数;提高性能和降低功耗 避免镜像抑制问题和不需要的混频产物;只需要基带上的一个LPF 高灵敏度(相邻通道抑制比[ACRR])图1显示了该系统的基本原理示意图,包括集成自动增益控制(AGC)环路的级联中频可变增益放大器(VGA),以及紧随其后的正交解调器、具有可变基带增益的可编程低通滤波器。图1中以灰色显示的元件( ADF4350 和 AD9248) 是为清楚起见,并不包括在系统级测量中(有关这些器件的详情请参见“常见变化”部分)。

理想情况下,第一级的输入和最后级的输出应设置系统的动态范围(信噪比)。实际上,情况可能并非如此。在正交解调器之前放置级联VGA不仅会给系统带来更多增益,而且有利于整体系统噪声性能,只要VGA的噪声系数低于正交解调器,只要VGA仍具有增益,且未发生衰减。后续级的噪声系数通过初始VGA的增益进行分频处理。提供VGA (相对于仅提供固定增益放大器)的另一优点是AGC环路可经设计以调平正交解调器的输入信号。这一限制施加于正交解调器和任何后续级的信号电平的能力非常重要。

中频VGA和AGC环路

中频VGA和AGC环路功能可通过 ADL5336来实现。它具有两个可级联VGA,每个VGA具有24 dB的模拟动态范围,并且可以通过SPI端口以数字方式改变每个VGA上的最大增益。

为了实现信号调平AGC功能,每个 ADL5336 VGA具有平方律检波器,通过可编程衰减器连接到输出。检波器将衰减器的输出与63 mV rms的内部基准电压进行比较。如果衰减器输出与63 mV rms基准电压间有差异,误差电流便会产生并集成到CAGC电容内。AGC环路通过将DTO1/DTO2引脚连接到GAIN1/GAIN2引脚关闭。为了使AGC环路正常工作,将MODE引脚拉至低电平,从而产生负VGA增益斜率。

每个 ADL5336 VGA具有允许的输入功率范围,AGC将在此范围内调平至特定设定点。在该范围以外,VGA输出随输入一起按dB递增或递减(假定VGA未处于压缩状态或信号不在噪底内)。

IQ解调器

信号从 ADL5336 路由至 ADL5387,在此接受解调并将频率转换为零中频。 ADF4350 频率合成器可向 ADL5387提供所需的2×LO信号(参见“常见变化”部分);但实际测试使用信号发生器代替 ADF4350 。

ADL5387 使用两个双平衡混频器,一个用于I通道,一个用于Q通道。提供给混频器的LO使用2分频正交分相器生成。这为I和Q通道提供了0°和90°信号。 ADL5387在RF输入至基带I和Q输出之间提供约4.5 dB的转换增益。

低通滤波器、基带VGA和ADC驱动器

低通滤波、基带增益和ADC驱动器功能全部使用 ADRF6510来实现。施加于 ADRF6510 的信号现在具有独立的I和Q路径,信号首先通过前置放大器放大,然后进行低通滤波,以抑制任何不需要的带外信号和/或噪声,最后通过VGA放大。

ADRF6510 的每个通道可分为三个级:

前置放大器 可编程低通滤波器 VGA和输出驱动器通过GNSW引脚,前置放大器具有6dB或12dB的用户可选增益。低通滤波器可通过SPI端口设置为1MHz至30MHz的转折频率,步进为1MHz。VGA具有50dB增益范围,增益斜率为30mV/dB。VGA增益通过GAIN引脚控制,GNSW引脚被拉低时范围可为0.5dB至+45dB,GNSW引脚被拉高时范围可为+1dB至+51dB。输出驱动器能够将1.5Vpp差分电压驱动至1k负载内,同时保持高于60dBc的HD2和HD3。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)