随着科技的进步,嵌入式系统的功能逐渐由简单向复杂发展,开发难度也随之提高。嵌入式 *** 作系统的使用,屏蔽了部分硬件信息,提供给开发者统一的平台,降低了开发难度,提高了代码的重复利用率。在一些特殊的领域(医疗、汽车、航空航天),对嵌入式系统的实时性要求非常高。在这些场合,任务必须在给定的时间内响应并正确完成。而实时 *** 作系统RTOS(Real TIme OperaTION System)本身的运行,必然会引起性能的下降,在任务数量增加时,这种下降更加明显。例如,使用uC/OS-II实时 *** 作系统在PowerPC处理器上运行,在TImeTIck(时钟节拍)周期为10 ?滋s、运行64个任务的情况下,TimeTick中断函数占用的CPU时间已达到42%[1]。

目前,RTOS软件层面的研究已经很成熟,可有效提高RTOS性能的方法有以下几种:

(1)提高处理器的运行频率[2]。这对功耗相当敏感的嵌入式系统并不是好方法。同时高频时钟所引起的电磁干扰对电路板布线的要求也更高;

(2)设计专用于RTOS系统服务的硬件。硬件对相同的 *** 作可并行处理。如果设计一种硬件,在任务数量或TimeTick频率增加的情况下,系统也能在固定的时钟周期内完成所有任务域的更新,从而降低RTOS运行所占的CPU时间。

本文设计了实时系统加速RTA(Real-Time Acceleration)模块,对任务调度和系统时间管理进行硬件化,降低了任务中断时间,并对最终的测量数据进行对比,得出结论。

1 RTA的硬件设计

本文的硬件平台使用OR1200[3] CPU,它是一款由OpenCores网站维护的开放源代码CPU,内部结构可见可修改,且没有版权问题。RTA模块作为从设备连接到Wishbone总线[4]上。在RTA模块中,由硬件实现任务管理和时间管理。RTA中的寄存器全部映射到内存空间上,软件通过对寄存器的访问来控制RTA模块的运行。

该专用硬件可分成如下两部分:

(1)任务管理和时间管理部分。RTA模块支持64个任务,使用基于优先级的调度策略,每个任务有唯一的优先级。RTA只在需要任务切换时才中断CPU。时间延时的最小单位是TimeTick(时钟节拍),最长时间延时可达65 535个TimeTick;

(2)用于产生TimeTick信号的Timer(计时器)。RTA必须有独立的Timer为其产生TimeTick信号。在本文中,利用OR1200自带的Timer完成此工作。

本文使用的系统是在μC/OS-II实时 *** 作系统基础上改进实现的。该RTOS由Micrium网站维护,已经应用于商业产品[5]。整个软硬件的实现在FPGA开发板DE2-70上完成,系统时钟频率为25 MHz。

1.1 任务管理和时间管理

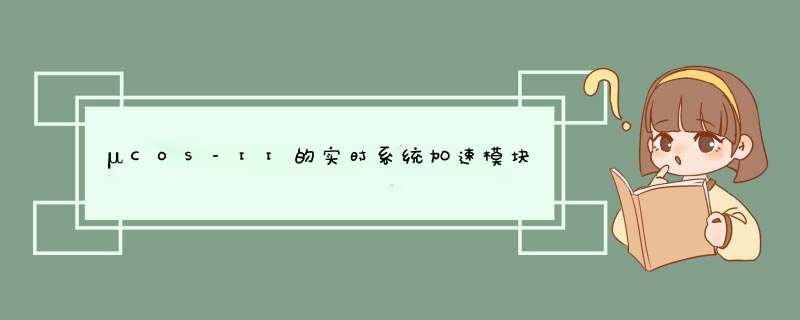

任务管理和时间管理的设计框图如图1所示。

每个任务都有4个域:TaskValid、OSTCBStat、OSTCBDly和OSTCBStatPend。每个任务都有一个任务就绪标志TaskReady,RTA通过PrioBitmapToBinary模块找到最高的优先级并送给HighestPrio。在CPU响应外部中断或者给调度器上锁时,可以通过OSIntNesting和OSLockNesting寄存器关闭RTA的中断。

μC/OS-II实时系统内核中,任务调度基于TimeTick完成,由于程序只能顺序执行,任务的timedly域更新也是顺序执行的,从而使得调度函数的执行时间与运行的任务数量有关。在RTA模块中,基于TimeTick的调度机制并没有改变,只是原型中顺序执行的timedly更新,在硬件中可以同时执行。在使用RTA模块的系统中,移去了软件中的用于任务调度的数据结构,相应地在硬件中予以实现。

当有更高优先级的任务进入就绪态时,就会产生RTA中断。硬件实现上,当进入就绪态的上个时钟周期的最高优先级和本时刻的最高优先级不同时,便产生中断信号。在μC/OS-II中,每个TimeTick时刻都会发生中断,这就需要更频繁地保存CPU寄存器,相比本文提出的方法,浪费了更多的CPU时间。

1.2 TimeTick信号的产生

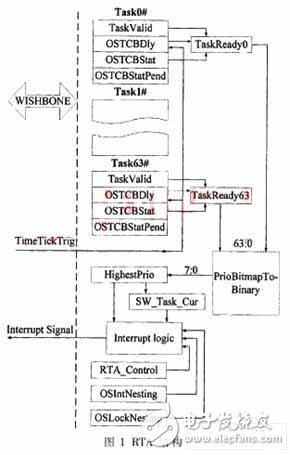

RTA的运行需要一个可配置的Timer来为其产生TimeTick信号。在本文中,通过对OR1200进行改造,利用其内部的Timer产生中断信号作为RTA任务调度的标准时钟节拍,而将RTA的中断信号连接到原来Timer在CPU的接口处。这样,CPU通过Wishbone总线可对Timer进行读写,且RTA产生的中断不会占用可编程中断控制器PIC(Programmable Interrupt Controller)。改造后的框图如图2所示。

1.3 软件实现

因为任务数据结构的改变,源码中所有涉及到任务数据结构的函数都要进行修改。由于任务调度和时间处理由RTA模块执行,原先执行TimeTick的中断函数要作相应修改,在中断时,只需读取RTA中HighestPrio寄存器,然后做上下文切换,运行该优先级的任务即可。

2 实验结果

本实验使用的CPU为OR1200,CPU和所有的外设都通过Wishbone总线连接,系统时钟为25 MHz。在Altera的Cyclone II FPGA平台上,使用Quartus8.1工具对RTA进行布局布线,其共占用4 197个逻辑单元LE(Logic Element)。

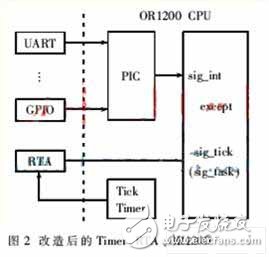

任务响应时间是RTOS性能的一个重要指标,其定义为:从任务中断产生的时刻起,到恢复任务执行之间的时间。试验中,利用自定义的Timer作为测量标尺,在2个测试点各读取一次,相减后的数值再乘以此Timer的周期,便得到该段测试时间。图3是有硬件加速和无硬件加速的任务响应时间的测试结果,单位是系统时钟周期。

从图中3可以看出,在无硬件支持的RTOS中,随着任务数的增加,任务响应时间也随之呈线性增加。其原因是,程序顺序执行,在无硬件加速的情况下,RTOS内核在每个TimeTick中断都要对任务的延时域进行顺序更新。随着任务的增加,延时域的处理时间也增长。有硬件加速支持时,任务响应时间缩短,而且与正在运行的任务数量没有关系。这是因为所有任务的延时域都同时更新,在一个时钟周期内即可全部完成。所以使用RTA模块后,降低了系统本身占用CPU的时间,提高了系统的可预测性。可见,在添加RTA模块后RTOS的性能得到了提高。

本文将μC/OS-II系统中调用频繁的任务调度和时间管理采用硬件实现,达到了降低系统负载、稳定任务响应时间、提高系统可预测性的目的。实验结果表明,使用本硬件,任务中断响应时间可降低85.8%。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)