DDS信号发生器采用直接数字频率合成(Direct Digital Synthesis,简称DDS)技术,把信号发生器的频率稳定度、准确度提高到与基准频率相同的水平,并且可以在很宽的频率范围内进行精细的频率调节。采用这种方法设计的信号源可工作于调制状态,可对输出电平进行调节,也可输出各种波形。

DDS原理在介绍DDS信号发生器原理之前我们先了解一下DDS原理。

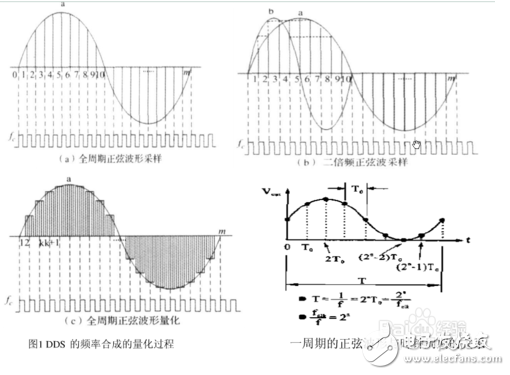

若对一正弦波形进行采样,每周期为 m 个采样点,分别记为 1~m。 对应每次参考时钟 f c , 输出一个采样点,输出图中所示的一个周期的正弦,需要 m 个时钟周期,则输出的波形频率为 f a =f c/m。对于这种情况, 每次时钟到来时,相位累加器加 1 ,则就会在第 i 个时钟周期输出 第 i 个采样点( i = 1~m) ,第 m + 1 个时钟输出第 1 个采样点,以此循坏,这时的相位累加器实 际上是步进为 1 的模 m 计数器。 如果每次时钟到来时, 总是间隔一个采样点输出,即相位累 加器的步进为 2 ,这时在第 i 个周期输出第 2i 个采样点,输出波形如图 1. 2 的波形 b,显然波 形 b 的频率是 a 的 2 倍,即 f b = 2 f a 。

综上所述,如果相位累加器的步进为 B, 则输出波形的频率为 B×f a , f a 是最小的输 出频率称为频率分辨率或步进间隔, B 为频率控制字。给定不同的频率控制字即可输出不同 的频率。频率输出公式为: f 0 = fc/m* B

在实际设计中,如果累加器长度为N ,则可以有2N 个存储单元存储采样数据,如果我们 对一个周期的波形进行2N 个点的采样,即m = 2N , 此时输出频率f o 和系统时钟频率f c ,相 fc f0 = N B 2 位累加器长度N 以及频率控制字B的关系为: 为了使波形输出不失真,根据奈奎 斯特定理, B最高为2 N - 1 。另外要提高DDS 的精度,就需要分母越大越好,即采样点的个数 越多,越接近实际波形。但实际上不可能提供如此之多的存储空间,这就需要对采样点进行量 化。如图1 (c) 所示,如果量化单位为K,则前K 个点的值总是相同的,为采样值1 ,第二组K 个 采样点的值为采样值2 ,以此类推,第i 组K 个采样点的值为采样值i , 共需要m/K个存储单元 来存储m/K个采样点。

DDS 的杂散来源之一就是相位累加器相位舍位造成的杂散。现有的频率控制主要采用 二进制频率控制原理。这是因为 FPGA 采用二进制的数据处理机制以及波形存储器的二进 制寻址方式,所以通常情况下 mK、m、K 都是二进制整数,如 m = 2^N ,这就要求对计算结果 进行十进制近似取舍,造成了波形发生器的输出频率以及频率分辨率存在无法消除的误差。

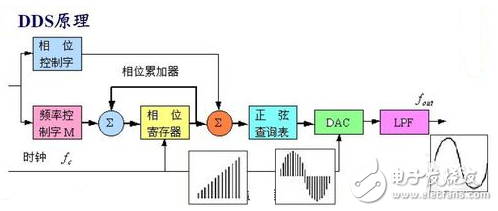

DDS 以数控振荡器的方式,产生频率、相位可控制的正弦,电路包括了基准时钟源、相位累加器、相位调制器、正弦ROM 查找表、D/A 转换 器和低通滤波器等。 频率控制字N 和相位控制字M 分别控制DDS 所输出的正弦波的频率和相 位。DDS 系统的核心是相位累加器,它由一个N 位累加器与N 位相位寄存器构成。时钟脉冲每触发一次, 累加器便将频率控制数据与相位寄存器输出的累加相位数据相加, 然后把相加后的结果送至相位寄存器的数据输入端。 相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端, 以使加法器在下一个时钟的作用下继续与频率控制数据相加。 这样, 相位累加器在参考时钟的作用下将进行线性相位累加, 当相位累加器累加满时, 就会产生一次溢出, 以完成一个周期性的动作, 这个周期就是DDS 合成信号的一个频率周期, 相位累加器的溢出频率就是DDS 输出的信号频率。 相位寄存器的输出与相位控制字相加, 结果作为正弦查找表的地址。 查找表由ROM 构成, 其内部存有一个完整周期正弦波的数字幅度信息, 每个查找表的地址对应正弦波中的一个相位点。 查找表把输入地址信息映射成正弦波幅度信号, 同时输出到D/A 转换器的输入端, 通过D/A 可将数字量形式的波形幅值转换成所要求的合成频率模拟量形式信号。 低通滤波器用于衰减和滤除不需要的取样分量, 以便输出频谱纯净的正弦波信号。

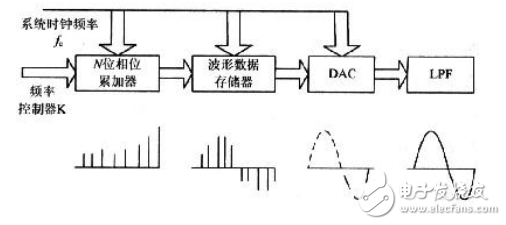

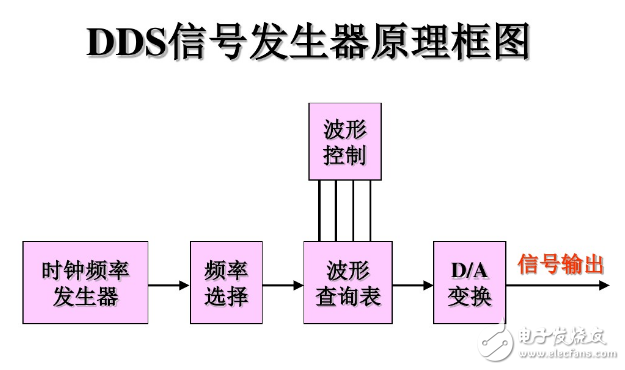

DDS信号发生器原理是建立在采样定理基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后通过查表读取数据,再经D/A转换器转换为模拟量,将保存的波形重新合成出来。DDS基本原理框图如图所示。

除了滤波器之外,DDS系统都是通过数字集成电路实现的,易于集成和小型化。系统的参考时钟源通常是一个具有高稳定性的晶体振荡器,为各组成 部分提供同步时钟。频率控制字(FSW)实际上是相位增量值(二进制编码)作为相位累加器的累加值。相位累加器在每一个参考时钟脉冲输入时,累加一次频率,其输出相应增加一个步长的相位增量。由于相位累加器的输出连接在波形存储器(ROM)的地址线上,因此其输出的改变就相当于查表。这样就可以通过查表 把存储在波形存储器内的波形抽样值(二进制编码)查找出来。ROM的输出送到D/A转换器,经D/A转换器转换成模拟量输出。

编辑推荐:四十种DDS信号发生器资料专题

1、方案设计与论证

设计的DDS信号发生器系统以STC89C52芯片为核心控制,通过可编程放大电路实现了正弦波、方波的输出功能,其频率步进值和幅度步进值达到了设计要求。

本设计采用直接数字频率合成。单片机从键盘获得控制信息,控制两路DDS芯片AD9850产生的两路设定频率的正弦波和方波。输出信号经过调整后输入AD7524可以在单片机的控制下完成对信号的程控误差。从DDS模块输出的两路信号经过低通滤波和直流偏置将两路信号输入模拟乘法器AD835,一路作为载波,一路作为调制波,从AD835产生调制波。同时可以将DDS信号输入到CD4046B芯片进行振荡输出调频信号。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)