整合的时钟电路,是硬件技术进步的一个标志。

电脑中的不同设备对时钟频率的要求是不一样的,如果你从废物箱中找来一块286主板,可以看到有好几颗晶振排列在一起。

电脑中的CPU,AGP插槽、PCI插槽、硬盘接口、USB端口和PS/2端口等在通信速度上有很大差异,所以需要提供不同的时钟频率,譬如PCI要求33MHz、USB为48MHz等(图6)。

可是,一只石英振荡器只能提供一种频率,所以主板制造商通常将这些原本散布在主机板上各处的振荡电路整合成一颗“频率合成器(Frequency Synthesizer)”芯片,对晶体振荡器产生的脉冲信号进行分频(或倍频),以便为不同运行速度的芯片(或设备)提供所需要的时钟频率。

图1: i875P主板上各种设备的速度

普通分频器为整数分频器,其输出频率与输入频率之间为整数倍的关系,只能分段调节频率,不能满足精密调节的要求。

频率合成器是“分数分频器”,可对输出频率进行精细调节。研发工程师可自由地设计电路中的各种频率,不再受限于石英震荡晶体的固定频率规格。

目前电脑中的时钟芯片一般都具有“分数分频”能力,可以根据需要将调节步长设计到1%,甚至0.1%。

为了指导和规范频率合成器的设计和应用,Intel制定了频率合成器设计指南,如CK97、CK40X等,适用于最新PenTIum 4处理器的规范是CK410。

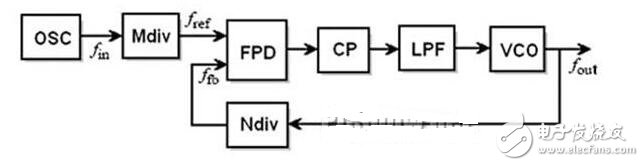

频率调节原理频率合成器是一个具有频率负反馈的时钟信号系统(图7),其中使用了两个分频器,Mdiv用于降低基准频率,Ndiv则用于对VCO进行分频。

晶体振荡器(OSC)产生的频率fi经M分频器后得到参考频率fref,它与反馈频率ffd分别送入鉴频器(Frequency Detector,FD)的两个反向输入端,

鉴频器输出一个反映两者之商的直流电压,并经低通滤波器(Low Pass Filter,LPF)滤除交流分量后,提供给压控振荡器(Voltage Controlled Oscillator,VCO)输出频率信号fout。

图2: 频率合成原理图

频率合成器的输出频率fout与输入频率fin之间的关系可以用公式fout=fin×(N+k/M)来表示,其中N、M和K均为整数,K可取0~M间的任意整数。

非整数值N+k/M通常写作N.F,这里的圆点代表小数点,N表示频率的整数部分,而F=k/M则表示频率的小数部分。

在输入频率fin、N和M均不改变的条件下,只要修改k值即可得到所需要频率值fout。

在频率合成器芯片中,有专门的SMBus接口电路,这是芯片的寄存器与外部联络的途径,有了它,就能够通过BIOS或软件对寄存器进行改写。

频率寄存器中的每一位数据有两种可能,“0”或“1”,那么当这几位按不同状态进行组合时就可得到多种外频输出。

频率合成器的频率调节精度与频率寄存器的位数有关,譬如,如果频率寄存器为5位,则调节步长为1MHz。为数越多,调节精度越高。

在实用的频率合成器中,Mdiv和Ndiv两个分频器均为可编程的,只要用户设定相应的fout数值,BIOS便能自动给出N、M和K的值,并通过SMBus总线写入相应的寄存器中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)