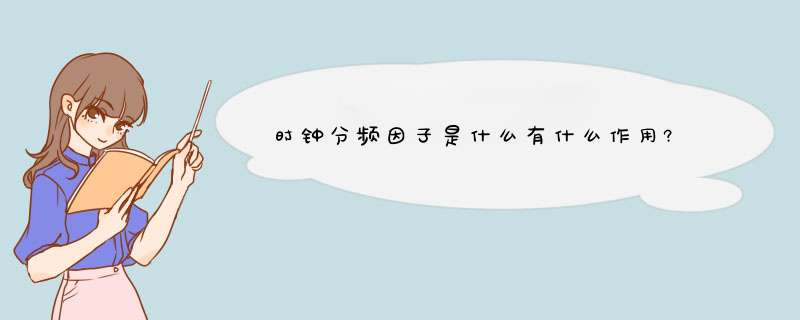

单片机都是有时钟振荡器的。还有定时器,看门狗,程序计数器等等。如果看门狗或者定时器所要求的脉冲速度比较时钟脉冲慢,那么,就要利用分频器进行分频,以得到你所要求的脉冲速率。

分频因子就是在定时器时钟进入定时器后设定一个分频因子,从而得到一个频率fDTS和时间值tDTS,这个频率和时间值主要用于上面说的三个地方。(并不是所有内部都用到,换句话说就是即使你设置了分频因子也可能用不到)

简单的说就是分频因子是通过对CK_INT的分割来确定tDTS的!

分频因子只是分频的手段,它的目的就是得到tDTS!

而tDTS主要用于,死区 用于死区发生器的采样时钟 和数字滤波器,也就是它要作用于这三个东西上。

我们再来看它的结果(就是设定了这两位引发的结果),只有一个就是给出了tDTS的值。好多人不理解就出在这个问题上,tDTS是什么呢,它其实就是一个时间值,这个值会用于下面说的三个地方。但实际上除了用到tDTS以外,还用到的是一个频率值fDTS。手册上也没有一个地方说明这点。当我们得到tDTS的值就等于知道fDTS,明白了这点就好理解了。

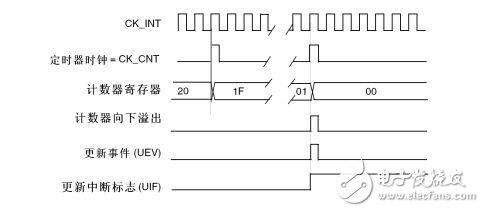

三种不同的时钟源可被用来驱动系统时钟 (SYSCLK)

HSI振荡器时钟

HSE振荡器时钟

PLL时钟

一般用的是PLL时钟,后面有证据。

我们可以通过库函数获取各时钟值

void RCC_GetClocksFreq(RCC_ClocksTypeDef* RCC_Clocks)

在我的系统里,把时钟值打印信息如下:

SYSCLK:0x44aa200 //72000000, 72MHz

HCLK:0x44aa200 //72000000, 72MHz

PCLK1:0x2255100 //36000000, 36MHz

PCLK2:0x44aa200 //72000000, 72MHz

ADCCLK:0x2255100 //36000000,36MHz

RCC-》CFGR:0x001D040A //PLL输出作为系统时钟

可推测几个预分频值为

AHB prescaler = 1

APB1 prescaler = 2

APB2 prescaler = 1

ADC prescaler = 2

根据读取RCC-》CFGR寄存器值为:0x001D040A,上面推测完全正确。

CFGR寄存器的SWS段也说明:PLL输出作为系统时钟。

TIM2使用PCLK1,但注意时钟树里有这一段

已知APB1 prescaler=2,故TIM2CLK = PCLK1*2 = 72MHz.

所以被TIM2分频的时钟大小是72MHz。

我的程序也证明了这点

TIM_TimeBaseInitTypeDef tim2_InitStruct;

TIM_DeInit(TIM2);

RCC_APB1PeriphClockCmd(RCC_APB1Periph_TIM2, ENABLE);//Enable Timer2 clock.

NVIC_ConfigurationForTimer2();

// PCLK1=36MHz, PSC=36000-1, CK_CNT=36MHz/(PSC+1)=1000

// ARR=2000, 1s/1000 * 2000 = 2s.

tim2_InitStruct.TIM_Prescaler = 36000-1;

tim2_InitStruct.TIM_Period = 2000-1;

tim2_InitStruct.TIM_CounterMode = TIM_CounterMode_Up;

tim2_InitStruct.TIM_ClockDivision = TIM_CKD_DIV1;

tim2_InitStruct.TIM_RepetitionCounter = 0;

TIM_TimeBaseInit(TIM2, &tim2_InitStruct);

TIM_ClearFlag(TIM2, TIM_FLAG_Update);

TIM_ITConfig(TIM2, TIM_IT_Update, ENABLE);//Enables the specified TIM interrupts.

功能描述

时钟结构:主时钟源来自外部晶振XTlpll或外部时钟EXTCLK。时钟源选择:通过OM[3: 2]的高低电平选择,现在我们采用00。OM[3:2]的状态在nRESET的上升沿锁存。尽管MPLL在上电复位后就开始工作,但是MPLL输出不作为系统时钟,只有对MPLLCON写入适当的数值后才可以。即使用户不想改变MPLLCON的值,也要重新写一遍才能使其起作用。

时钟控制逻辑:时钟控制逻辑决定要使用的时钟源,当锁相环被设置为一个新的值时,时钟控制逻辑切断FCLK直到PLL输出稳定。时钟控制逻辑在上电复位或从power_down状态启动时使能。上电复位:注意上电后必须通过设置PLLCON才能使PLL作用。在正常 *** 作状态下改变PLL设置:通过改变PMS的值来实现。USB时钟控制:UCLK不起作用直到UPLL被设置。

FCLK、HCLK、PCLK:可以通过HDIVN、PDIVN、CLKDIVN来改变3种时钟的比率,推荐采用1:2:4的比率。在设置完PMS的值后,需要设置CLKDIVN寄存器,该寄存器设置的值在PLL锁定后生效,只需要1.5个HCLK即可完成比率的修改。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)