模数转换器(ADC)很久以来一直是通信接收机设计的基本器件。随着通信技术的不断发展,消费者要求更快的数据速率和更低的服务价格。提供这项技术的回程服务供应商面临着两难的处境。更高的数据速率意味着更多带宽,这也就表示更快的数据转换器,将模拟无线电波转换为数字处理。然而,更快的数据转换器(GSPS,或称每秒千兆采样转换器)——广为人知的有RF采样ADC——同样产生大量数据,而这些DSP芯片必须以高得多的速度进行处理。这无疑增加了无线电接收机的运营成本。

解决方案是对组成RF采样ADC的硅芯片进行更优化设计。得益于硅芯片工艺的进步(感谢摩尔定律),定制型数字处理模块中的RF采样ADC在功耗和尺寸方面的效率相比现有FPGA要更高。使用这些数字信号处理模块还能获得更低的数据速率,从而可以使用成本更低的FPGA。这对于运营商来说是双赢的局面,因为他们可以使用这些GSPS ADC以高频率进行采样、使用内部数字下变频器(DDC)以所需速度处理数据,并以能实现的(低)数据速率将其发送至更为廉价的FPGA(或者现有的ASIC产品)进行进一步的基带处理。

使用带有DDC的RF采样ADC的另一个优势是,这样可以通过更灵活、更紧凑、性价比更高的方式实现双频段无线电系统。双频段无线电系统的应用已有多年历史。基站系统设计人员以前通过使用两个独立的无线电路径(每频段一个)来实现双频段无线电系统。本文讨论一种利用多频段无线电接收机——使用RF采样ADC,比 如AD9680——对两个独立而使用广泛的频段进行数字化和处理。本文第一部分解释了功能框图级别的实现,并讨论了双频段无线电系统中使用GSPS ADC的优势。本文第二部分将讨论TDD LTE频段34和39(亦分别称为频段A和频段F)的实现和数据分析,并通过数据分析来揭示显示器性能。

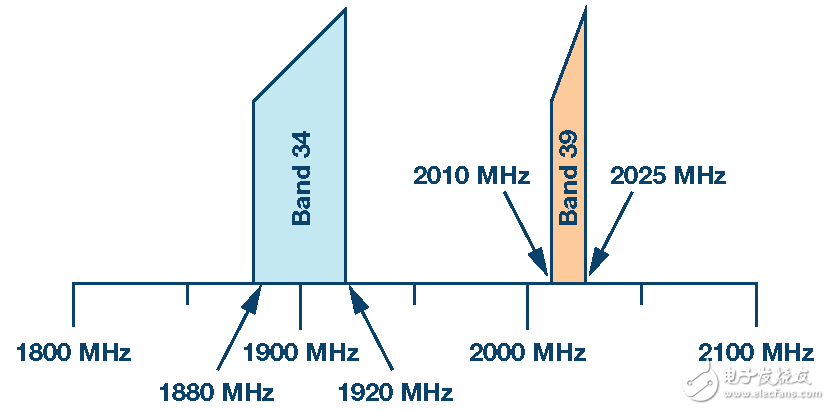

传统双频段无线电接收机为了迎合客户对于双频段无线电的需求,同时满足总系统级性能要求,基站设计人员拿出了他们的看家本领:复制两次无线电设计,然后每频段调谐一个设计。这意味着针对客户的选择,设计人员必须将两个独立的无线电硬件设计调谐至两个频段。

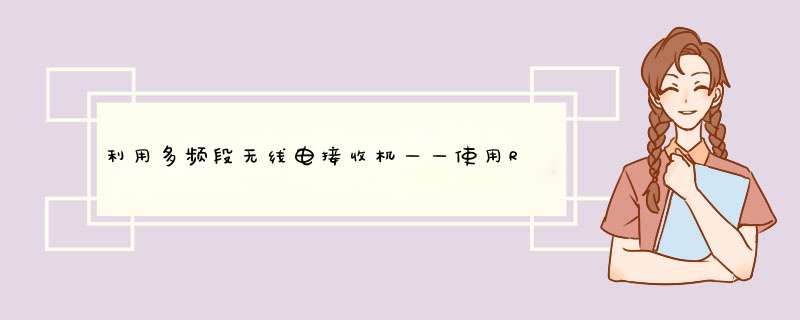

例如,如果需要构建能支持TDD LTE频段34(频段A:2010 MHz至2025 MHz)以及频段39(频段F:1880 MHz至1920 MHz)1的无线电接收机,则设计人员就会打包两个无线电接收机设计。TDD LTE频段的频率规划如图1所示。

图1. TDD LTE频段34和39的频率规划。

设计双频段无线电接收机以支持这些频段的传统方法是部署两个独立的接收机链路,每频段一个。下文图2显示了双频段无线电接收机的框图。

图2. 双频段无线电接收机设计的传统方法。

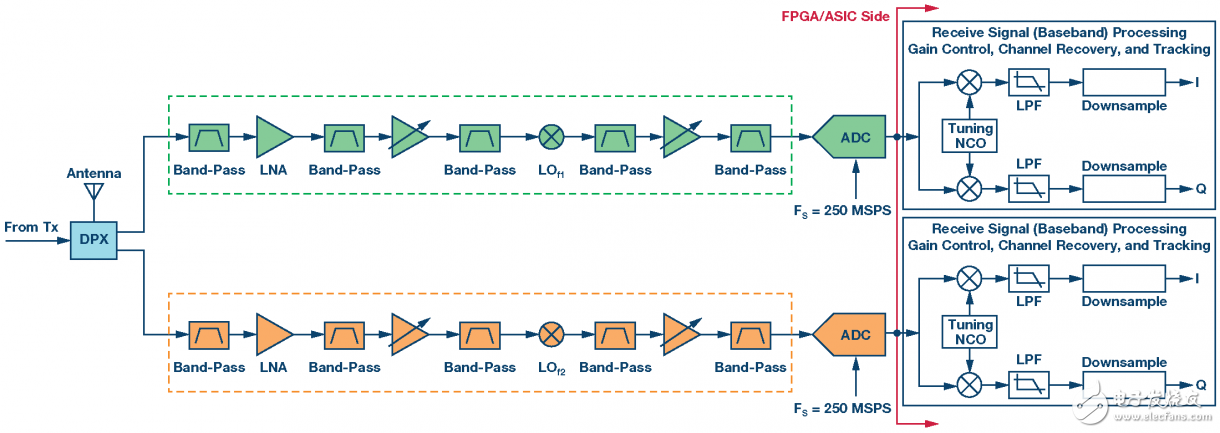

图3. 传统双频段无线电接收机的FPGA接口要求。

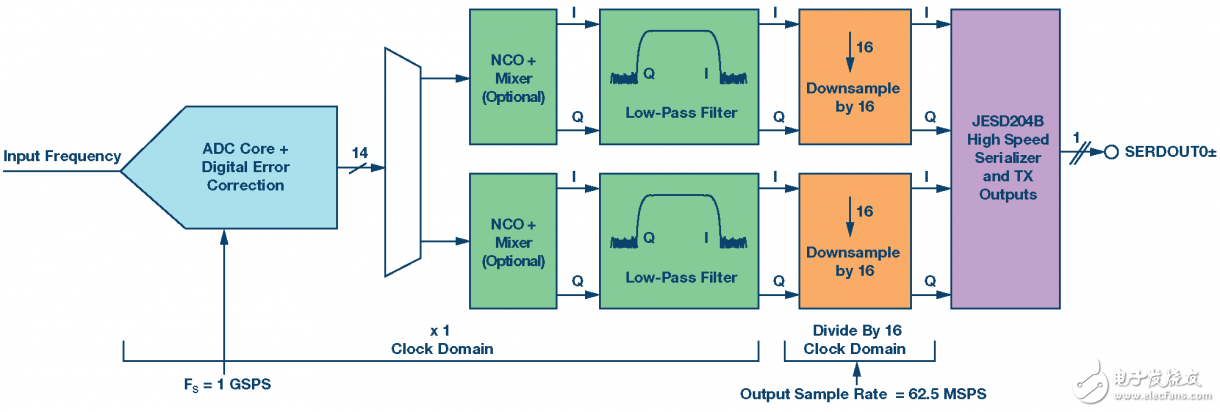

使用RF采样(GSPS) ADC的双频段无线电接收机RF采样或GSPS ADC能够提供系统设计灵活性。利用深亚微米工艺技术,GSPS ADC可以集成数字处理模块,且相比FPGA以低得多的功耗进行特定速度下的数据 *** 作。RF采样ADC的核心是一个高带宽模拟采样内核,以GHz速度进行采样。模拟内核之后是各种各样的数字信号处理元件。这些数字下变频器可以用来提取相应频段。针对双频段接收机设置的RF采样ADC内部框图如图4所示。DDC除了处理信号,还可降低JESD204B通道数据的通道速率。

图4. 显示内部DDC的RF采样ADC框图。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)