摘 要: 现场可编程逻辑门阵列(FPGA)应用于图像处理时,需要对数据中的图像信息进行准确的提取。设计中,FPGA中解压缩功能需要对压缩数据中的图像信息进行提取。根据压缩格式,设计了一种基于状态机的图像信息提取模块,并且在XST(Xilinx官方综合工具)以及Synplify pro两个综合环境下进行了仿真验证。通过对比仿真结果的差异,尝试分析设计的寄存器传输级视图(RTL视图),并找出了影响状态机工作的关键要素。强调了代码风格对FPGA设计的重要性。

0 引言

状态机是数字系统设计中的重要组成部分,是FPGA实现高效率高可靠性逻辑控制的重要途径。在实际工程应用中,状态机工作是否正常决定着系统能否稳定工作。本文设计了一个基于状态机的图像信息提取模块,通过对该设计的仿真,分析了状态机设计中的状态竞争、锁存器的引入以及综合工具误判等常见情况。强调了代码规范对于FPGA设计的重要性。

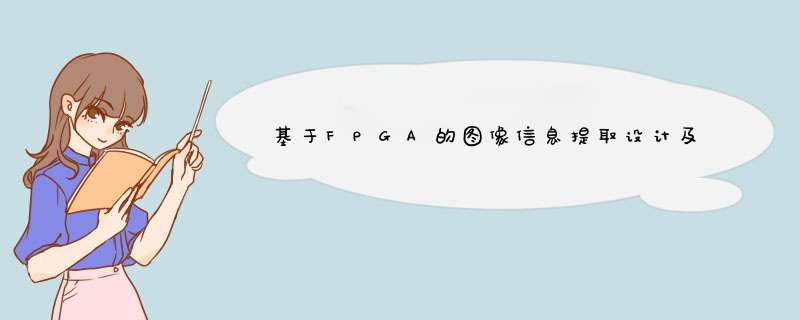

1 设计背景及思路基于相机的实时图像目标仿真系统可以产生实时的虚拟目标图像流,因而被用于光电经纬仪等图像跟踪系统的开发调试。目标仿真系统中虚拟目标是经过DSP以一定的压缩格式压缩后储存于DDR中的,FPGA通过SRIO与DSP通信,读取压缩后的目标图形数据,经过FPGA内部解压缩与现实背景叠加输出。该系统中使用灰度图像作为图像源。其简化结构图如图1所示。

目标图像示意图如图2所示,虚拟目标图形以水平方向的线段形式压缩,整个压缩后的目标图形由n条线段组成,每条线段包含该线段的起始行列号、像素点数以及各像素点的像素值。其中每一帧的第一条线段还包含这帧图像压缩后的大小,压缩大小为32 bit。行列号、像素数以及各像素点的像素值均以16 bit表示。

FPGA对虚拟目标图像进行复原时,最主要的是对压缩数据中的目标图形的各类信息进行提取,行列号代表着目标图形的位置信息,压缩大小以及像素数表示目标图形的大小信息,像素值则代表各点的灰度信息。本文以有限状态机为基础设计了基于状态机的压缩图像信息提取模块。

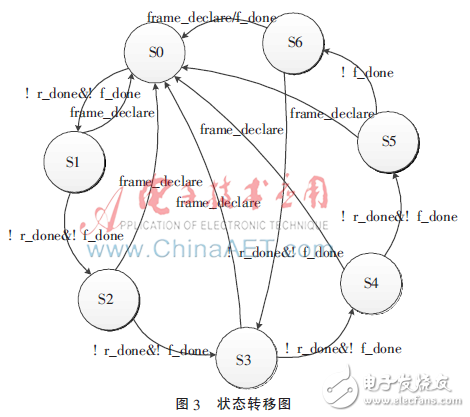

首先需要确定状态机的状态数。压缩图像信息提取模块的目的在于将压缩图像的信息进行分别提取,因此根据压缩的数据格式须将数据分为5块进行提取,分别为一帧压缩图像大小(frame_size,32 bit)、每条线段的起始行号(row_no,16 bit)、起始列号(column_no,16 bit)、每条线段的像素数(row_size,16 bit)以及分别的像素值(pic_element,16 bit)。考虑到16 bit的位宽,须将一帧压缩图像大小(frame_size)进行两次提取,由于空闲状态的存在,共设置7个状态,分别为:wait_state(S0)、frame_s_state1(S1)、frame_s_state2(S2)、row_no_state(S3)、column_no_state(S4)、row_s_state(S5)、pic_element_state(S6)。

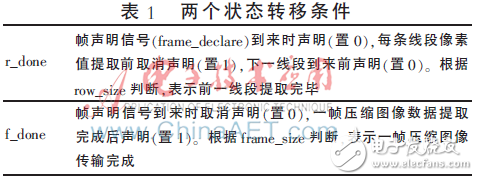

需要注意的是压缩数据中frame_size只存在于第一条线段,因此frame_size的提取在一帧数据中只进行一次。根据数据大小以及每行像素数,可以设置相应的状态转移条件,相应的信号如表1所示。

压缩数据在帧声明信号到来之后开始传输,当帧声明信号到来时,状态机进入等待状态(S0),随后便开始依次提取第一条线段中的信息,包括帧大小的前16 bit,帧大小的后16位,行号、列号、像素数(即依次进入S1、S2、S3、S4、S5状态),接着将r_done信号拉高,并且开始提取像素值数据(即进入S6状态)直至下一线段到来,第二条线段到来时r_done信号拉低,提取第二条线段的行号(即从S6跳转到S3状态),其余步骤与第一条线段相同,直至一帧信号传输完成(即f_done拉高),状态机跳转置等待状态(S0)。根据上述分析,状态转移图如图3所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)