介绍一种采用FPGA(现场可编程门阵列电路)实现SDH(同步数字体系)设备时钟芯片设计技术,硬件主要由1 个FPGA 和1 个高精度温补时钟组成.通过该技术,可以在FPGA 中实现需要专用芯片才能实现的时钟芯片各种功能,而且输入时钟数量对比专用芯片更加灵活,实现该功能的成本降低三分之一.该技术实现的时钟输出完全符合ITU-T G.813 标准,可广泛应用于各种SDH 设备中。

高速串行传输技术被越来越多的通信设备采用.高速数据传输对时钟的要求很高,而能满足高速传输需求的各种专业芯片不仅价格昂贵,而且功能单一,灵活性低,不能满足用户多样化的需求[1].不同线路输入的时钟经过长距离传输,信号质量劣化程度不同,经过FPGA 的SerDes(串并转换)恢复出来的线路时钟质量不同.除此外,SDH 通信系统接入的输入信号线路数量不定,时钟芯片需要对不确定数量的线路时钟进行保持跟踪.虽然有相应的专用芯片来达到上述的目的,但是针对不同数量的线路时钟,导致专用芯片的灵活性有所欠缺,且成本较高,如达拉斯公司的DS3100 时钟芯片,输入的时钟数量最多只有6路;IDT 公司的82V3399 芯片,输入的时钟数量最多只用8 路[2].本研究的目的就是要解决上述技术中存在的问题,使用FPGA 对SDH 中使用的时钟进行处理,完成时钟芯片功能。

1 系统硬件设计

系统硬件主要由2 部分构成:

1)19.44M 温补时钟:主要对FPGA 提供19.44M 高精度低抖动时钟信号.

2)FPGA:主要完成时钟的输入和输出,最终完成整个时钟芯片功能.

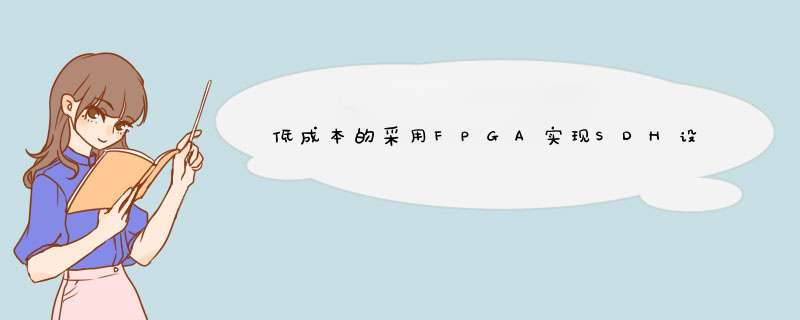

硬件及主要信号线连接示意图如图1 所示.

图1 硬件及主要信号线连接示意图

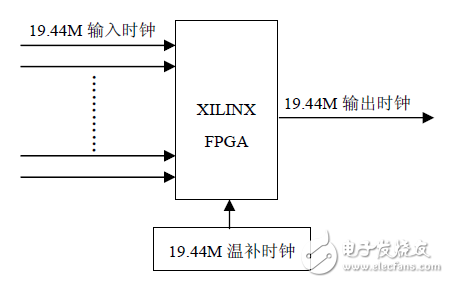

2 系统程序设计FPGA 设计中的主要功能模块如图2 所示。

图2 FPGA 内部功能模块示意图

FPGA 通过外部管脚和CPU 连接,CPU 通过提取各路SDH 信号的时钟质量开销符号S1 控制FPGA 从各输入时钟选择1 路作为19.44M 线路时钟,选择器由FPGA 内部查找表完成。

2.1 CK 模块(Clock,时钟模块)设计

CK 模块将19.44M 线路时钟和19.44M 输出时钟分别分频为8K 的时钟,为PD(Phase Detect,鉴相模块)模块提供鉴相输入信号.在本设计中,分频功能由FPGA 自带的锁相环实现.Virtex-6 系列FPGA 自带的锁相环输入和输出范围均为10~700MHz,接受抖动范围为0-10 UI[3],可以实现倍频、分频、移相等功能,输出时钟和输入时钟同相,且具有时钟锁定指示信号。

2.2 PD 模块(Phase Detect,鉴相模块)设计

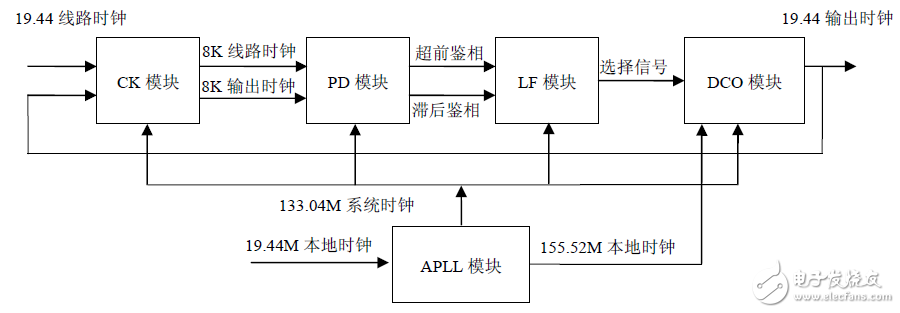

PD 模块对线路时钟和输出时钟进行鉴相,将指示线路时钟超前输出时钟的超前鉴相信号和指示线路钟时落后输出时钟的滞后鉴相信号输出给LF(Low Pass,低通模块)模块。有限状态机状态转移图如图3 所示。

如图3 所示,每个状态的输入由同一时刻采集的8K 线路时钟和8K 输出时钟状态组成.在空闲状态,当采集到输入为10 时,表示采集到8K线路时钟高电平,8K 输出时钟低电平,线路时钟超前输出时钟,进入超前状态,并输出超前鉴相信号;当采集到输入为01 时,表示采集到8K 线路时钟低电平,8K 输出时钟高电平,线路时钟滞后输出时钟,进入滞后状态,并输出滞后鉴相信号,其它输入保持空闲状态;在处于超前或滞后状态时,当输入为00 时,表示采集到8K 线路时钟低电平,8K 输出时钟低电平,进入空闲状态,当输入为11时,表示采集到8K 线路时钟高电平,8K 输出时钟高电平,进入暂停状态;在暂停状态,当输入为01时,表示表示采集到8K 线路时钟低电平,8K 输出时钟高电平,线路时钟超前输出时钟,跳转到超前状态;当输入为10 时,表示采集到8K 线路时钟高电平,8K 输出时钟低电平,线路时钟滞后输出时钟,跳转到滞后状态。

图3 PD 模块有限状态机状态转移图

2.3 LF 模块(Low passs,低通模块)设计

低通模块是低通滤波器。为了防止时钟抖动带给PD 模块错误的鉴相结果,LF 模块对PD 模块的输出进行低通滤波,滤除高频分量后输出正确的选择结果。在本设计中,低通模块主要由两个10 比特位宽的计数器组成,分别命名为超前计数器和滞后计数器。计数器阈值为1023.每次PD 模块发出超前鉴相信号,则超前计数器加1,当PD 模块发出滞后鉴相信号,则滞后计数器加1.当超前计数器记满1023 后,则复位超前计数器,并同时向DCO模块(Digital Control,数字控制)发出超前控制信号;当滞后计数器记满1023 后,则复位滞后计数器,并同时向DCO 模块发出滞后控制信号。

状态机采用格雷码编码,具体编码实现采用赛灵思公司推荐的硬线逻辑语言编码约束,详细代码如下:

Library IEEE;

Use IEEE.std_logic_1164.all;

EnTIty PD is

Port(

Prc_o : out STD_LOGIC;

Fal_o : out STD_LOGIC;

Clk_i : in STD_LOGIC;

8K_lne: in STD_LOGIC;

8K_out: in STD_LOGIC

);

Type state_type is (IDLE, PRCEED, FALL_BEHIND, PAUSE);

Signal c_s : state_type := IDLE;

Signal n_s : state_type;

Attribute fsm_encoding : string;

Attribute fsm_encondg of c_s : “gray”;

Process

Begin

Wait unTIl risign_edge(clk);

C_s <= n_s;

End process;

Process(c_s, 8K_lne, 8K_out)

Variable st : STD_LOGIC_VECTOR(1 downto 0);

Begin

St := 8K_lne & 8K_out;

N_s <= c_s;

End case;

When PRCEED | FALL_BEHIND =>

Case st is

When “00”=> n_s <= IDLE;

When “11”=> n_s <= PAUSE;

When others => NULL;

End case;

Case c_s is

When IDLE =>

Case st is

When “10” => n_s <= PRCEED;

When “01” => n_s <= FALL_BEHIND;

When others => NULL;

When PAUSE =>

Case st is

When “01”=> n_s <= PRCEED;

When “10”=> n_s <= FALL_BEHIND;

When others=> NULL;

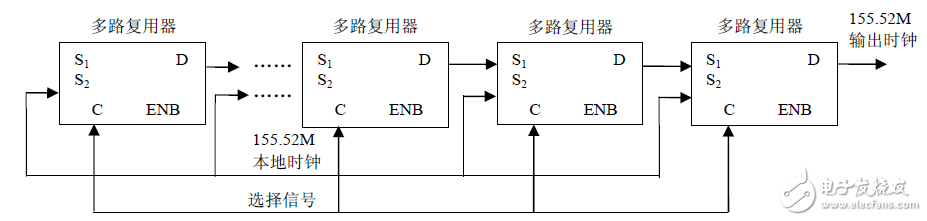

2.4 DCO 模块(Digital Control,数字控制模块)

DCO 模块控制本地时钟移相追踪线路时钟相位.把LF 模块输入的超前鉴相和滞后鉴相每22 秒加权平均进行统计,24 小时的统计结果存储在FPGA的块RAM中.在输入时钟丢失时,FPGA从块RAM 中顺序读出统计值,使输出时钟追踪线路时钟过去24 小时的相位变化[4].DCO 模块中的移相控制电路图如图4 所示,DCO 模块通过FPGA内部的多路复用器对155.52M的本地时钟移相。每个多路复用器提供π/14 个弧度相移。因为FPGA内部布线延时的不精确,所以本设计利用ISE自带的FPGA Editor手动摆放14个多路选择器在各自查找表中的位置及每个查找表在FPGA内部的位置,将抖动控制在0.4ns 以内[5],从而达到精确相移的目的。

图4 DCO 模块移相控制电路图

2.5 APLL 模块(Anolog Phase Lock Loop,模拟锁相环)设计

模拟锁相环调用FPGA 自带的模拟锁相环,通过本地高精度的19.44M 晶振,生成各子模块需要的311.04M 和155.52M 高速时钟。

经过系统联合调试,基于FPGA 的时钟芯片设计技术,时钟抖动控制在0.4ns 内,超过GR-253-CORE (OC-192) 和ITU-T G.813 (STM-64)的关于时钟精度要求。为SDH 业务板卡提供工作时钟960 h,工作正常,板卡没有出现误码、丢包现象,达到SDH设备应用的预期目标。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)