随着现场可编程门阵列(FPGA)应用变得越来越庞大和复杂,在进行一个费时的编译过程和使用高保真测试覆盖进行设计调试之前,仿真对验证IP变得越来越重要。在NI LabVIEW软件里,你能为函数和时序仿真你的应用逻辑。周期精确仿真通过提供一种验证您的逻辑信号传播的方式来测试您的应用的时序限制。这些仿真器同时使你有能力测试您整个的FPGA应用,集成您的LabVIEW FPGA 和组件级IP (CLIP)或者IP集成节点逻辑。本白皮书注重于第三方周期精确仿真器与LabVIEW FPGA的集成。 获取更多关于LabVIEW FPGA的函数仿真功能的信息,请参考LabVIEW FPGA 在线帮助。

1. 使用LabVIEW以及第三方仿真器进行协同仿真您的FPGA应用的协同仿真能够使您有能力直接利用LabVIEW建立和执行仿真,从而提供最高水平的虚拟,同时仍旧可以在后台利用成熟的第三方周期精确仿真器。

在协同仿真中,LabVIEW向处于测试阶段的IP提供激励,控制仿真器的执行,以及捕捉反应。利用LabVIEW协同仿真,一个驱动输入和执行(通过常规FPGA上位机接口功能实现)的上位机VI替代传统的基于VDHL的测试平台。这种虚拟的测试平台,通过使用您已掌握的LabVIEW技能提高生产效率,同时,无需VHDL专业知识就能在您的LabVIEW FPGA VI上研制和执行周期精确仿真。

图1. LabVIEW FPGA中的周期精确协同仿真免除了对VHDL专业知识的需求,并且无需对LabVIEW所编写的测试平台。

每一个FPGA上位机函数的执行决定了第三方仿真器何时执行仿真的下一部分。例如,当LabVIEW 上位机 VI中的写入属性节点函数执行时,它向模拟器传达适当的激励并推进模拟进行时间。一旦仿真器计算出结果,它中断运行同时等待下一条来自于LabVIEW的控制命令。

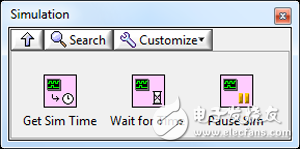

为了实现模拟器执行的额外的控制和灵活性,仿真FPGA上位机接口函数选板提供诸如检索当前仿真时间、强制仿真等待指定时间、或者暂停仿真器运行等函数。

图2. 仿真FPGA上位机接口函数选板针对第三方仿真器执行时间的提供了更细分的控制函数。

使用LabVIEW测试平台的协同仿真现在仅受Mentor Graphics公司的仿真器支持。获取详细步骤指南,请查阅使用LabVIEW和 Mentor Graphics ModelSim的周期精确协同仿真。

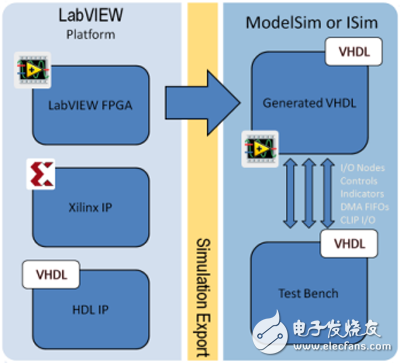

2. 生成用于第三方仿真器的仿真输出用于周期精确仿真的第二方法(即基层方法)是生成和输出在第三方仿真器中直接使用的LabVIEW FPGA仿真。与协同仿真相比,这种方法要求一个基于VHDL的测试平台从而提供激励、控制和测试执行,以及捕捉/验证输出。其结果是,结合LabVIEW FPGA使用这种方法时,你必须熟悉HDL 仿真器和 VHDL。使用这种方法的优点在于,与Mentor Graphics ModelSim(仿真器)相比,你可以将这些位于LabVIEW FPGA中的仿真文件输入Xilinx Isim周期精确的仿真器。

图3. 通过修改由LabVIEW建立的测试平台,您能够在ModelSim 或者 Isim.中执行周期精准仿真。

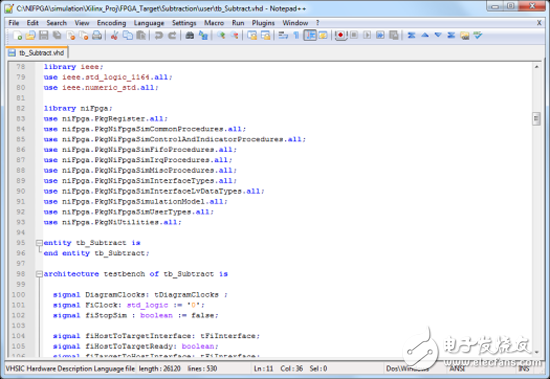

作为仿真输出的一部分,LabVIEW为您的FPGA应用生成一个测试平台文件模板。在此基础上,您能够增加特殊的VHDL代码用来适当地调整您的设计。

图4. LabVIEW生成一个VHDL测试平台模板作为仿真输出文件的一部分,从而加速您的测试平台研发。

欲知如何生成仿真文件、编辑测试平台,以及在Xilinx Isim中运行仿真,请参考详细步骤指南 使用Xilinx ISim进行周期精确仿真。

3. 结论为了在编译和部署之前高效率地仿真您的FPGA应用,LabVIEW FPGA向函数和周期精确的 时序仿真提供了工具。周期精确的仿真器能够找出并行代码间的重要信号传输冲突和相互干扰。传统情况下,这就需要特殊专业技能和时间投入,远超出原始IP研发的时间。

LabVIEW FPGA中的周期精确的协同仿真使用Mentor Graphics ModelSim,免除了对VHDL专业技能的要求,同时,通过利用您现有的LabVIEW技能极大地减少了测试平台研发时间。

LabVIEW FPGA自带一个免费的周期精确的仿真器,Xilinx Isim。但即便这样,LabVIEW生成的VHDL测试平台模板仍需要您有能力进行进一步修改,从而恰当地调试设计。

使用LabVIEW 2011 FPGA 模块,更加有效地学习FPGA代码开发。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)