在使用每秒千兆次采样(GSPS)模拟数字转换器(ADC)时,促使相同系统中多重转换器同步化的需求与之相同非常重要,然而速度以及接口让这件事难以达成。

使用确定性延迟或是JESD204B接口数据字组当中的控制位两种方法,都是JESD204B Subclass 1的特点。

事实上,多重ADC同步化在航天与国防工业当中是一项基本要求,因此市面上的ADC为能够促进多重转换器同步化,会兼具12位、2.5GSPS等特性,并以此做为该组件的标准特点。

同步化的定义是能够只依据ADC的孔径抖动、频率抖动及频率分配精确度,而使每个转换器匹配至相当于或是低于单一频率周期精确度的能力。目前,新款ADC主要采用符合标准JESD204B接口技术的高速串行数据信道。

时间戳利于大量转换器同步化

其实,以JESD204B为基础的转换器在市场上仍然是相当新的组件,许多用户第一次采用此项技术对同步化多重组件的能力多所顾虑。然而,若使用简单的平台测试设定,进而将两组转换器同步化并展示其可扩展性,应该就可以纾解部分或是所有顾虑。

要将多重GSPS转换器一起同步化有两种独特选项。第一种方案是使用确定性延迟,其中的延迟必须要针对个别独立的数据路径加以调整,藉以修正时序的不匹配。

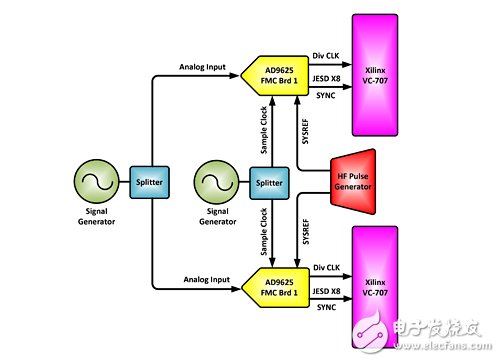

图1 测试设定及其主要相互连结方块图

第二种选项使用一般被称为「时间戳」的方法。其不须要量测每一个转换器到每一个现场可编程门阵列(FPGA)的时间延迟,对于大型系统而言特别重要,因为可能会有架设于地面的雷达系统得使用数百个转换器的潜在需求。

会因同步化而受益的关键性应用就是雷达。在这种案例当中,绝对的时间量测结果是不需要的,设计者只须要考虑从一组接收组件到下一组组件的相对时间即可。

图2 AD9625 FMC电路板w/同步链接

在使用时间戳时最后的数据处理比较没有那么密集,因为FPGA或是处理器只需要在每组数据集合中搜寻一个时间标记,透过这个时间标记可以让设计者针对每颗转换器路径从经过定义与同步化的点去将数据对齐,毋须担心在大量转换器/FPGA对组中,每颗转换器到各自FPGA走线长度的距离。此路由甚至可能会穿过多重电路板,使其在应用设计当中更有帮助。

业界近期推出的ADC使用的是对于如何执行此同步方法相当重要的Subclass 1。Subclass 1使用SYSREF讯号来对齐串联输出数据;将频率置入转换器的输入数据当中,这样的安排让SYSREF能够与转换频率同步,并且确保每组分配的SYSREF讯号会在相同时间送达每组转换器。

这将会产生出一个要放置于JESD204B串联输出数据中的标记或是时间戳,藉以显示出同步数据分析应该要开始的确切点。

图3 电路板链接至开发平台上的FMC1、HPC插槽。

当然,新组件会提供两种使用这个标记的选项。设计者可以使用整个16位JESD字组中任一部分的独立控制位,或是以SYSREF时间戳取代转换器的最低有效位(LSB)。值得注意的是,这些控制位的执行及用来将多重转换器同步化的方法并非JESD规格的一部分,在JESD字组中每个控制位的命名则留给每个独立转换器设计去斟酌,而且在不同转换器之间可能会有所差异。

相位匹配缆线确保频率同步化

图1的设定显示如何将两颗转换器同步化。然而理论上来说,能够加以同步化的转换器数量是没有限制的,以经过适当设计的转换器电路板开始(图2、图3),有关于测试的设定需要如下的设备。

‧ 执行Windows *** 作系统的标准桌上型/笔记本电脑

‧ 开发工具包

‧ FMC电路板,如AD-FMCADC2-EBZ

‧ 脉冲产生器及激发系统

‧ 讯号产生器w/选项B22、低相位噪声选项

‧ 使用于频率与SYSREF连结的24GHz匹配RF缆线

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)