有鉴于软件定义无线电(SDR)平台是实现5G等先进通讯系统不可或缺的工具,半导体厂推出专为SDR应用量身打造的新一代捷变(Agile)收发器射频芯片,其整合模拟讯号处理与强大滤波功能于小巧且低功耗组件中,可大幅简化SDR平台设计复杂度并提高实际运算效能。

对于成功且实时的捷变(Agile)无线电收发器设计而言,高性能、宽带优化转换器及相关的高速现场可编程门阵列(FPGA)是必要的元素,但是许多设计者还需要额外的资源;由于组件有其复杂性,所以独立运作或是接近独立运作的方式不再可行,起因是内部连结的格式与通讯协议,以及电路板布局的细微之处所致。

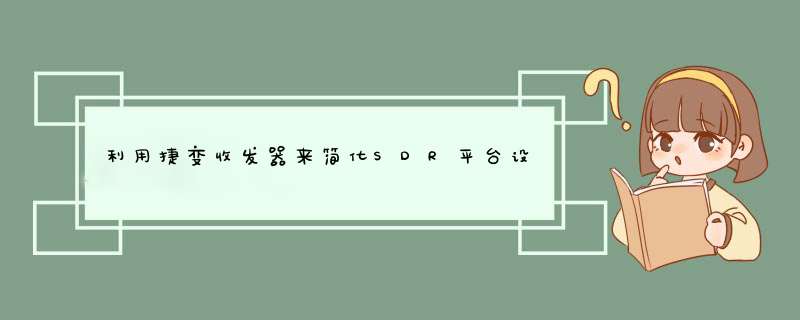

软件定义无线电(SDR)平台通常需要多项技术才能真正建立出一个完整的解决方案,其中包括射频(RF)与模拟数字转换器(ADC)设计、数字硬件、系统单芯片(SoC)汇编语言、数字信号处理器(DSP)硬件,以及软件开发技术等;要克服这些技术落差的其中一个方法就是使用参考设计及支持工具(图1),例如可以在完成一项工作范例时提供协助的MATLAB。

图1 RF开发工具--FMCOMMS1-EBZ的模拟前端适用于宽广范围运算密集,以及以FPGA为基础的无线电应用,包括SDR在内。在与FPGA开发平台结合时,该RF开发工具能够实现从基频到RF的各种物理层的无线通信功能。

SDR借力参考设计 滤波器设计挑战有解

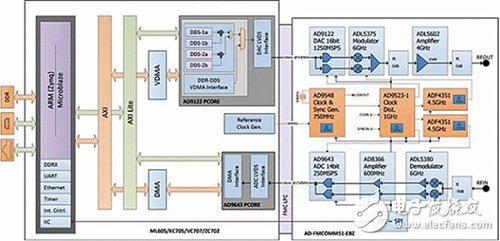

举例来说,有一项常见的SDR挑战就是设计可编程滤波器。在SDR平台当中有可编程的TIA滤波器、低通滤波器、数字半波段滤波器,以及可编程有限脉冲响应(FIR)滤波器,而每个滤波器都会对组件链当中的下一个滤波器造成冲击;因此当某项功能不能运作时,设计者会发现很难找到问题所在。

使用参考设计时,设计者可以看到不同的滤波器级并了解每个滤波器级如何在通带中产生出独特的振幅下滑与群组延迟,了解独特的振幅下滑与群组延迟是如何发生以及发生于何处之后,设计者可以针对FIR滤波器当中的延迟加以补偿,并在数字基频装置中建立一个平坦的频带响应(图2)。

图2 SDR系统功能方块图

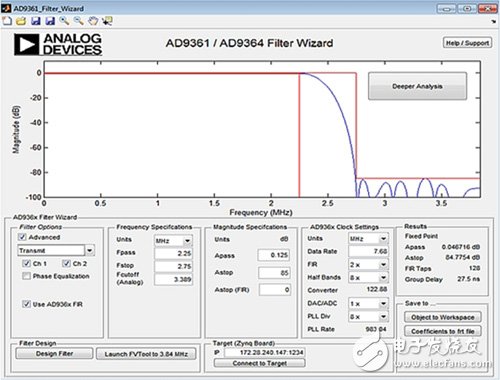

另一项设计者所将面临的挑战就是如何设计FIR滤波器,使其能够针对前面各级累积的所有影响而加以补偿。针对此一需求,有一个小型的滤波器设计MATLAB App(图3),可以用来设计发射器与接收器FIR滤波器,协助设计者将来自于滤波器链中其他模拟与数字级的强度,以及相位响应纳入计算。

图3 由MathWorks所开发的MATLAB,可以应用于无线SDR系统与组件中复杂滤波器的设计。

透过挑选具备合适规格的组件,来获得评估工具、应用支持、参考设计,以及第三方知识与产品,开发团队将更有可能符合他们的多重设计目标,以及成本与时间指标。

无论系统工程师较喜欢使用FMC或是商业用的SDR平台,藉由支持工具与资源所获得的好处将会使系统工程师赢得先机。

新型收发器实现次世代SDR平台

值得注意的是,大量无线标准各有其不同的频率、带宽、通讯协议、格式,虽为使用者带来前所未见的连结与存取能力,但这同时也代表无线系统工程师在设计或是调查问题、性能、选项时,将会面对严苛挑战。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)