ZYNQ7000与传统FPGA有着巨大的差异,它将自己定位为一款All Programmable Soc(软硬件可编程片上系统),视其为以FPGA作为外设的双核ARM A9处理器更加准切。它的启动过程体现了以处理器为核心这一特点,以往植入处理器硬核的FPGA的启动过程是先启动逻辑部分,再启动处理器,ZYNQ7000相反,先启动处理器再启动逻辑部分。

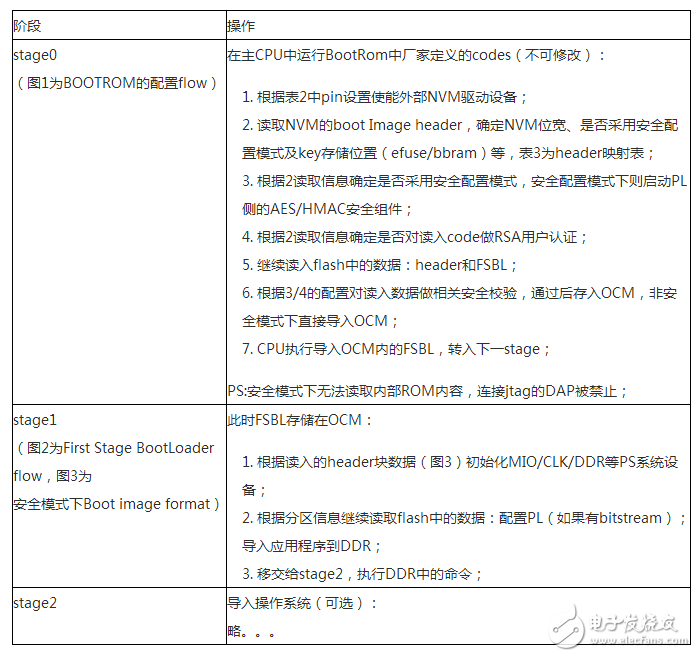

一、ZYNQ7000配置过程ZYNQ7000的配置按先后顺序分为3个阶段:stage0、stage1、stage2(可选)。

表1:配置步骤

表2:boot模式引脚映射

表3

图1

图2

图3(UG821)

二、ZYNQ7000安全策略ZYNQ7000提供诸多安全防范模块供客户调用,根据模块的特性可以分为被动和主动两类,被动模块主要包括多种加密、认证策略,主动模块包括JTAG关闭、温度电压监测、代码一致性检测、特异性检测(器件DNA)等,表4详细地列出这些部件,客户可根据设计需要调用。

表4:主被动防护模块

主被动模块相互配合完成工程的安全设计,以下对常用的部分安全策略进行简介。

(1)、RSA用户认证:

在某些情况下,设备对程序来源的合法性有很高要求:必须由合法的组织提供的程序才能启动设备,以确保设备工作在设定的情景中,任何非法程序或对合法程序的篡改将无法让设备工作。Xilinx Z7芯片提供的RSA用户认证功能即是为了满足对程序进行合法性认证而引入的。

RSA是一种非对称加密技术,将其与数字签名技术配合使用,就能对相关数据的合法性进行认证。

Xilinx采用2组公私钥,1组固定,1组可替换,由此来确保更高的安全性。固定的1组称为PPK/PSK(primary public key/primary secret key),替换组为SPK/SSK(secondary public key/secondary secret key)。

需要做认证的数据在其后加入1段认证代码,其包括:PPK,SPK,PSK加密SPK后得到的SPK签名,SHA-256摘要算法对FSBL做摘要,得到的摘要用SSK进行加密获得签名,此签名也存放到认证代码,因此,认证代码包含上述4块数据。

RSA认证过程是对认证代码携带的信息进行 *** 作。首先使用SHA-256算法对PPK进行摘要,得到的摘要与存储在EFUSE中的值作对比,一致则进入下一步;认证后的PPK队SPK签名进行解密,对比解密后的值与SPK,一致则进入下一步;SPK解密FSBL签名,同时对FSBL进行SHA-256摘要获取,对比摘要与SPK解密值,一致则RSA认证结束。

(2)、AES加密与HMAC代码认证:

Xilinx Zynq-7000通过芯片内嵌的AES-256解密引擎和HMAC (Keyed-hashed message authenTIcaTIon code)认证引擎来保护客户的知识产权,防止拷贝、抄板等损害客户知识产权事件的发生。

基本原理:Xilinx Zynq-7000内含AES-256解密引擎和HMAC认证引擎,并支持Secure Boot启动方式,用于保护客户的设计(包括软件的二进制可执行代码,数据以及FPGA的bitstream编程文件)不被窃取和使用。

客户在完成设计后,可以使用Xilinx ISE软件为设计添加用于认证的256-bit的校验码,然后再用256-bit密钥AES算法进行加密。256-bit AES密钥由客户生成,保存在FPGA内部,不能被外部读取。启动时,Zynq-7000首先执行芯片内部ROM中的代码。BOOTROM代码首先通过AES-256解密引擎对对被保护的设计进行解密,然后通过HMAC引擎认证完整性,只有通过认证的设计才能被加载并执行。

对于试图通过“抄板”窃取知识产权的行为,因为缺少和FLASH内容相对应的AES密钥,FLASH中内容将不会被加载并执行。256-bit AES密钥对应的组合达到1.15×1077种,可以充分保证客户知识产权的安全。

Xilinx Zynq-7000内含的硬件安全引擎的特点:

1. HMAC硬件认证引擎 在内层保护客户设计不被非法篡改,保证客户设计的完整性。

使用美国国家标准技术研究所的SHA256 FIPS PUB-182-2算法和HMAC FIPS PUB-198算法,这些算法由美国国家标准技术研究所(NaTIonal InsTItute of Standards and Technology, NIST)提供,签名保存在Boot Image中。

2. AES-256硬件解密引擎 在外层保护客户设计不被反向工程,不被分析破解,不被拷贝。密钥保存在片上的eFuse或者BBRAM(battery-backed RAM),不能被JTAG或者FPGA逻辑读取。eFuse仅支持一次可编程,掉电内容不丢失。BBRAM可支持反复编程,但是掉电内容丢失,因此需要外接电池。

AES算法是美国国家标准技术研究所和美国商务部的正式标准。Xilinx支持最高安全等级的256-bit密钥加解密方式。

256-bit AES密钥可以由用户指定,用Xilinx BitGen工具生成加密的bitstream,也可以由工具生成随机密钥。AES密钥由Xilinx iMPACT软件通过JTAG写入Zynq-7000芯片中。写入AES密钥时,所有FPGA中的存储器(密钥存储器和配置存储器)都会被清空。密钥写入后,没有任何办法可以重新读出写入的密钥,也不可能在不清空全部存储器的情况下改写密钥。当采用BBRAM保存密钥时,需要在VCCBATT上外接电池,确保系统掉电的情况下BBRAM中的内容不会丢失。系统正常工作时,由VCCAUX对BBRAM供电,而不会使用VCCBATT上的电池供电。当系统掉电时,VCCBATT需要的电流很小(nA级别),一块手表纽扣电池可以使用很长时间。

在secure boot模式下,PS DAP和PL TAP控制器被关闭,这样排除了通过JTAG访问芯片内部的可能。 PS的DAP控制器可以通过eFuse的JTAG CHAIN DISABLE永久关闭。在生成PL bitstream时,可以配置DISABLE_JTAG选项,禁止通过JTAG访问PL。

(3)、特异性检测(DNA等):

每片XILINX芯片都有唯一的57bit串行码对应,称之为芯片的DNA,特异性检测使能时,检测电路会对比基于内部串行码产生的CRC校验码和外部flash输入的校验码,一致才能启动设计。

由于每片芯片都需单独的生成配置代码,对于大批量生产不方便,为了解决这个矛盾,部分芯片内部提供了一片32bit的一次性烧写efuse,由用户自定义存入的32bit串行码,由此解决上述矛盾。

特异性检测的保护强度因其串行码位数限制,不及RSA、AES+HMAC认证。

(4)、电压温度监测:

ZYNQ7000内置温度和电压传感器,配合片上的AD,可以对芯片的温度和电压进行监测,非法读取或篡改内部信息常常伴随温度和电压反常,当变化值超过设定的上限时,我们可以选择擦除内部efuse或BBRAM保存的key;

(5)、JTAG关闭:

非法读取或篡改最常用的手段是通过JTAG口窥视片内程序,针对这一非法行为,XILINX器件可以通过多种手段关闭JTAG口,如efuse使能的永久性关闭、在代码内调用BSCANE2模块关闭,bitgen设置关闭。上述手段从物理上截断了窥视途径,同时也带来调试的不方便,一旦JTAG口关闭,必须使用其他的配置器件进行配置。

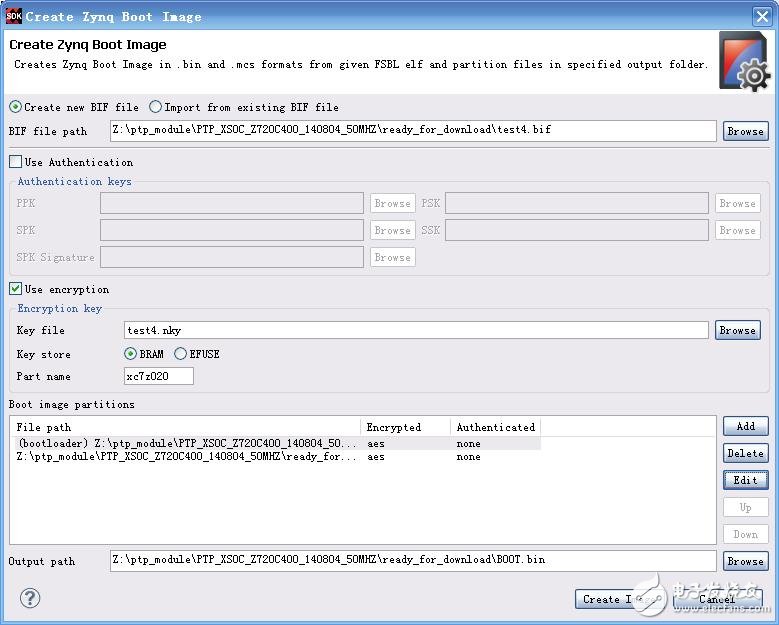

三、ZYNQ7000安全策略实践(1)、key文件生成

上图为使用sdk14.1生成image所需要填写的内容,如果key文件需要生成,在key file行填入key文件的文件名,key store选择存储介质,part name行填入工程选用的器件名如xc7z020,如果此处填写错误会影响到impact烧写。

添加FSBL文件时必须选择aes加密选项,否则sdk会报错,这是因为zynq是通过FSBL是否加密来决定是否调用解密模块,所以如果要生成加密image,那么FSBL必须为加密,同时,bitsream文件也必须加密,而其他的文件则可以自由选择是否加密;

(2)、KEY烧写

烧写至BBRAM时很简单,添加key文件至PL器件后,点击program即可,但烧写efuse时遇到麻烦,执行后报警告:

查看EFUSE烧写所需具备的条件如下:

These are the requirements for programming or reading the eFUSE registers using iMPACT:

• iMPACT is running on a PC with Microsoft Windows XP (32-bit) or Windows 7 (32-bit or 64-bit) OS.

Note Windows 7 64-bit support is only enabled for Zynq-7000 and 7 series devices.

• iMPACT is operating in Boundary Scan mode, and the unconfigured target FPGA device is in the chain in the Boundary Scan window.

• You are connected to the Boundary Scan chain through a Platform Cable USB II download cable.

• The Boundary Scan chain is operating at a cable speed of 3 MHz for Zynq-7000 and 7 series devices, 6 MHz for Virtex-6 FPGAs, or 1.5 MHz or slower for Spartan-6 FPGAs. To set the cable speed, run the command Output > Cable Setup and set the TCK Speed/Baud Rate option in the Cable Communication Setup dialog box.

• The target FPGA is not currently programmed. No bitstream information has been downloaded into the FPGA.

• The VCCAUX and VFS (Virtex-6 and Spartan-6 only) voltages supplied to the FPGA are set to the required levels. Voltages necessary for eFUSE reading and writing are described in the following user guides.

• For reading eFUSE registers, the VCCAUX voltage supplied to the FPGA must be set to the recommended operating condition. For programming Virtex-6 and Spartan-6 eFUSE registers, the VFS voltage supplied to the FPGA must also be set to its recommended operating condition. See the following data sheets for the recommended operating conditions of each power supply.

(3)、JTAG Debug

JTAG的存在方便了调试,但却留下了安全隐患,下面是如何禁止JTAG port的三种方法。

In Zynq-7000 AP SoC, the JTAG port is used to load software and the bitstream, load the AES key, control information, and for debug. If not disabled, JTAG ports can be used by an adversary to insert malware, and read configuration memory and registers. The JTAG ports must be disabled whenever it is not used in a legitimate debug operation.

The device can be debugged using a DAP controller and/or a JTAG controller. The DAP JTAG chain and PL JTAG chain can be concatenated or used independently. When used independently, the full SoC/FPGA does not need to be exposed to an adversary. For example, if debug only requires access to the PL, the user can select that only PL JTAG chain is used. This prevents access to the PS.

Zynq provides hierarchical control of the JTAG port. This allows different methods to control access to the debug ports based on security requirements. Security requirements may change over the life cycle the embedded device. There are three methods to disable the JTAG debug ports. Prior to fielding an embedded device with Zynq, a one-time programmable eFUSE bit can permanently disable access to the debug ports. Programming this eFUSE bit is irreversible, and debug ports remain disabled after powering down and recycling power.

The second method, which can be used only if the debug port disable eFUSE is not blown,disables/enables debug access port using the JTAG_CHAIN_DISABLE,DAP_EN,SPINDEN, SPIDEN, NIDEN, DBGEN bits in the Control register at 0xF 8 007000 (see Table 4). The debug access control is provided independently for the two JTAG chains or the concatenated chain.

In the third method, a lock register provides semi-permanent disabling of access to the debug ports. In this method, the debug port access disable remains in effect until a power cycle.In a secure boot, the JTAG port is disabled early by the BootROM code. Users who will not use the debug port after product release can disable the JTAG port permanently by writing the eFUSE Disable JTAG register. The disable is done using iMPACT or the Secure Key Driver.

Any attempted read or write access to the BBRAM via JTAG causes the BBRAM contents to be cleared and the entire configuration of the FPGA to be erased prior to access being enabled (i.e., being able to enter “key access mode”)。

(4)、加密策略

最高级别的加密时RSA校验与AES加密合并使用,目前我们仅选择AES加密方式。

AES加密的关键是key的保护,ZYNQ提供2种保密方式,BBRAM和eFUSE,BBRAM保密更安全,但维护稍显复杂,efuse熔丝保存方式可能会被物理破解,但这也需要相当的技术背景及专门设备才可以。因此,考虑各方面因素,选择EFUSE方式保存AES的key文件。

同时,因为JTAG口存在一定的安全隐患,可能被精通器件和相关背景知识的人员调用,进而读取KEY文件,因此在产品定型后永久性关闭JTAG口。

另一方面需要注意的是,由于ZYNQ产品即使烧写了KEY文件,但如果image启动文件为非加密方式,器件仍然能启动,对于了解这一特性的专业人员,他们可以加载一份非加密文件启动设备,然后在自己的代码里打开key的读取接口,窃取key文件后,再将加密文件破解。因此为防止此类窃取事件,我们设定只能从efuse加密方式启动(另一种方式是用RSA验证启动文件)。

总结我们的加密策略,EFUSE保存,JTAG关闭,仅从efuse加密启动。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)