JESD204B为业界标准序列通信链接,数据转换器与现场可编程门阵列(FPGA)、数字信号处理器(DSP)、特定应用集成电路(ASIC)等装置间的数字数据接口因此能化繁为简,这项标准减少装置间路由进而降低输入/输出及电路板面积需求,符合无线通信、量测、国防、航天等应用所需。

一般选择高速模拟数字转换器(ADC)时,ADC延迟高低大多并非重要设计因素或规格,最近新的JESD204B高速串行接口正迅速在全球普及,也逐渐成为数字接口首选,不过也因此为ADC延迟增加多个频率周期,故有些系统设计师仍继续沿用既有的低延迟接口,本文分析造成高速管线式ADC延迟的主因,并说明部分系统仍避免选用JESD204B的理由。

系统设计人员标示组件延迟时,通常以奈秒为单位,但管线式ADC延迟计算单位为频率周期,意指从ADC采样频率捕捉到输入讯号,至产生数字输出的时间差,采样率增加后,固定频率周期的绝对延迟奈秒数减少。

传输延迟(TPD)代表频率输入、频率输出与数据的缓冲延迟,一般未纳入延迟数据中,取决于缓冲使用量,以及个别缓冲击在不同制程、电压及温度下的延迟变化,故传输延迟属于变量,可能低于一个频率周期,也可能达到数个频率周期。

管线式ADC的产品说明书内,亦标明未纳入延迟数据的孔隙延迟,意指从输入采样频率的上升边缘抵达ADC,到采样实际发生之间的时间差。

分析管线式ADC延迟

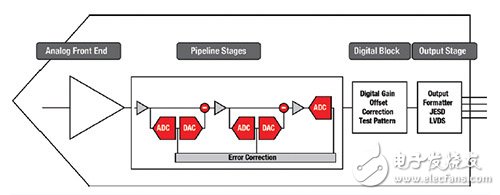

现代高速管线式ADC的延迟与设计大有关系,ADC可拆解为四项基本区块:模拟前端、管线级、数字区块、输出级(图1),由于ADC设计师可决定各区块配置情形,基于ADC采样率、耗能、AC效能等考虑因素,每一项设计都各有不同。

图1 现代高速管线式ADC的基本区块

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)