在小功率无线产品射频开关电路设计中,我们常常选用CMOS,GaAs,SOI等工艺的射频器件,其外围电路很简单,通常只需要配合电阻电容就可以正常工作。但是在大功率场合,设计工作就变得复杂起来,通常需要使用PIN Diode射频开关。无线时代在近期的一款大功率无线设备研发过程中,就使用了Skyworks的SKY12207-478LF PIN Diode开关,并为其设计了合适的驱动电路,通过调试,已经可以正常工作。

SKY12207-478LF主要特征

高功率,CW (ConTInue Wave)50W,峰值功率300W

低插入损耗,典型值0.4dB

高隔离度,42dB@2.6GHz

适用于TD-SCDMA,WiMAX,LTE基站等设备

SKY12207-478LF工作原理概述

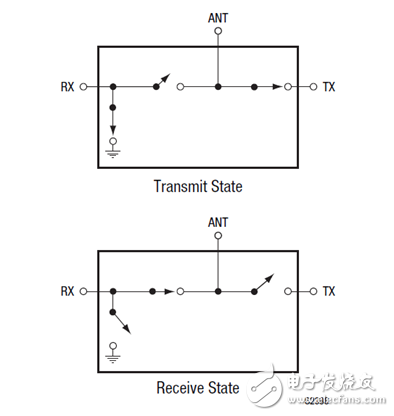

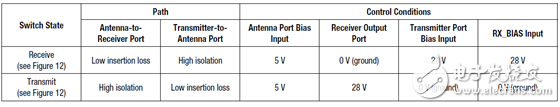

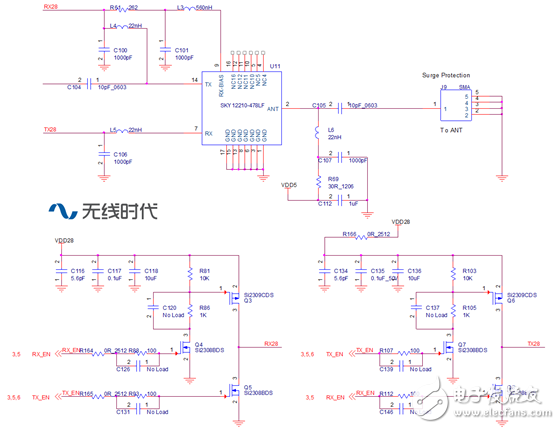

我们暂且不对SKY12207-478LF的细节工作原理做深入的探讨。下图是SKY12207-478LF的等效框图,其导通状态由加在ANT端的5V及TX/RX端的28V/0V偏置电压来决定,例如,处于发射状态下,TX设置为0V,而RX端设置为28V。

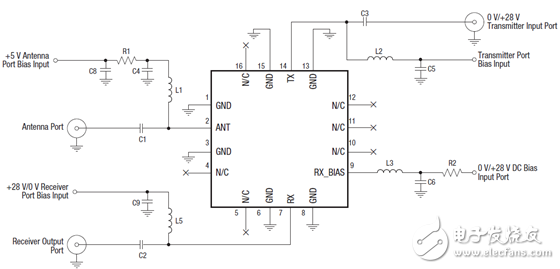

SKY12207-478LF的偏置电压为28V,这与功率管LDMOS的供电电压一致。Datasheet中给出了SKY12207-478LF的参考设计电路及对应的真值表。

那么,只要构建出符合真值表的驱动电路,就可以使SKY12207-478LF正常工作。

PIN Diode射频开关驱动电路设计

这个产品是无线时代网站之前提到过的超大功率射频功率放大器,驱动电路设计分析过程如下:

来自收发判别电路的逻辑电压为5V,用5V的逻辑电压实现对28V偏置电压的控制,MOS管是最佳选择

同样的端口(TX/RX/RXBIAS)可以提供28V供电,也可以实现对地短路,同时还可以可以提供合适的偏置电流

符合真值表的控制逻辑

Vds>50V,Ids>100mA

尽量选用封装尺寸较小的器件

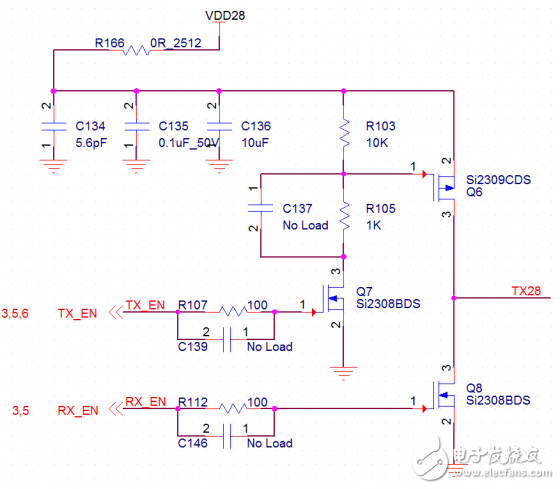

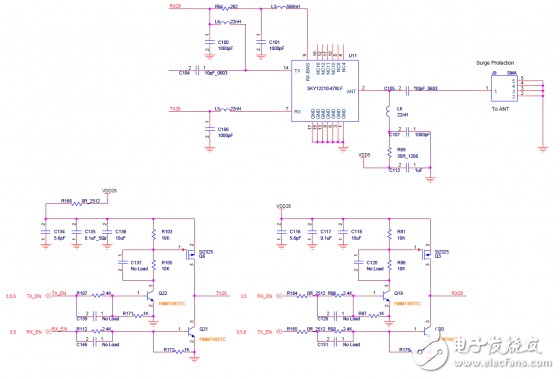

我参照了DCDC的开关电路,设计了如下的驱动电路,原理图中PIN Diode射频开关型号为SKY12210-478LF,与SKY12207-478LF pin-to-pin。其中,来自收发判别电路的TX_EN与RX_EN逻辑电平总是相反的,这样,Q3,Q5不能同时导通,Q6,Q8也不能同时导通。当然这种方法有一定的局限性,开关频率过高时可能会出现问题,很多电源芯片在这方面都做了特殊处理,本设计不做考虑。

驱动电路中使用了四颗NMOS与两颗PMOS,都是Vishay公司的SOT-23封装的MOS管。当来自收发判别电路的TX_EN为“1”时,RX_EN为“0”,Q5导通,Q4截止,Q3的Vgs=0,Q3截止,对应的RX28网络对地短路,即TX与RXBIAS端口均为0V;Q8的Vgs=0,Q8截止,Q7导通,Q6的Vgs<0,Q6导通,对应的TX28网络连接至28V电源,即RX端口为28V,符合真值表。当来自收发判别电路的TX_EN为“0”时,RX_EN为“1”时,MOS管导通/截止状态与上述过程相反,同样满足真值表。

PIN Diode射频开关驱动电路调试

在确定收发判别电路可以正确地给出逻辑电平之后,发现Q8特别容易损坏,很容易想到一定是有较大的电流流过Q8,才会这样。设计过程中已经仔细确认过,Si2308完全可以胜任1A以上的电流,而TX26与RX28网络都有限流电阻,流过Q8的电流不可能超过1A,那么唯一的可能就是Q6导通了!TX_EN为“0”时,RX_EN为“1”时,Q7正确地处于截止状态,Q6的Vgs=0,按理说Q6不可能导通,那么唯一的可能就是Q6有较大的漏电流。

从Si2309的Datasheet中仍然看不出问题,索性将Si2309更换为Si2305,同样是一颗PMOS,出现于TI的TPS23754 802.3at PD解决方案中,Si2305的典型特征是很高的工作电压,可以达到-150V。将Q3,Q6均更换为Si2305,PIN Diode射频开关SKY12207-478LF终于可以正常工作了。

在这次调试设计与调试过程中,无线时代充分融合了各个电路模块的设计调试经验,采用与DCDC类似的驱动电路,并使用了PoE电路中的高压MOS管,最终实现了对PIN Diode射频开关的驱动。在后来的研究中,发现有很多现成的PIN Diode开关驱动芯片,也有采用分立元件的方法,有兴趣的读者可以研究研究。

附:什么是PIN Diode

PIN二极管(posiTIve-intrinsicnegaTIve diode,缩写为PIN Diode),是在两种半导体之间的PN结,或者半导体与金属之间的结的邻近区域,吸收光辐射而产生光电流的一种光检测器。普通的二极管由PN结组成,在P和N半导体材料之间加入一薄层低掺杂的本征(Intrinsic)半导体层,组成的这种P-I-N结构的二极管就是PIN 二极管。

加负电压(或零偏压)时,PIN管等效为电容+电阻;加正电压时,PIN管等效为小电阻。用改变结构尺寸及选择PIN二极管参数的方法,使短路的阶梯脊波导的反射相位(基准相位)与加正电压的PIN管控制的短路波导的反射相位相同。还要求加负电压(或0偏置)的PIN管控制的短路波导的反射相位与标准相位相反(-164°~+164°之间即可)。

PIN Diode(二极管)射频开关驱动电路设计与调试续(2014年6月25日)

本文前几天提到的解决方案,在后来的测试中出现了问题,为了防止误导读者,我在此做出修正。

前文提到Si2309异常损坏,后经过仔细推敲,分析,发现有两方面原因,一是N-MOS在应该截止的时刻意外导通,二是Si2309的Vgs超过了其最大承受范围。

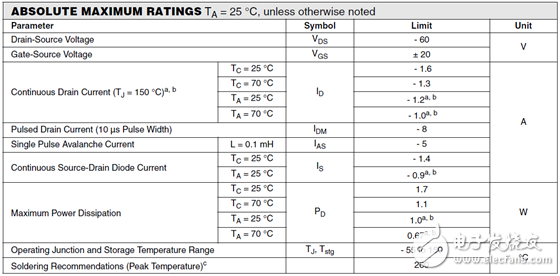

在下图中,当系统处于接收状态时,RX_EN应为逻辑1,TX_EN应为逻辑0,按照正常计算,当TX_EN为逻辑1时,A7导通,Q6的Vgs=28*(1/11 – 1)= -24.5V,超出了Si2309 Datasheet中+-20V的范围。

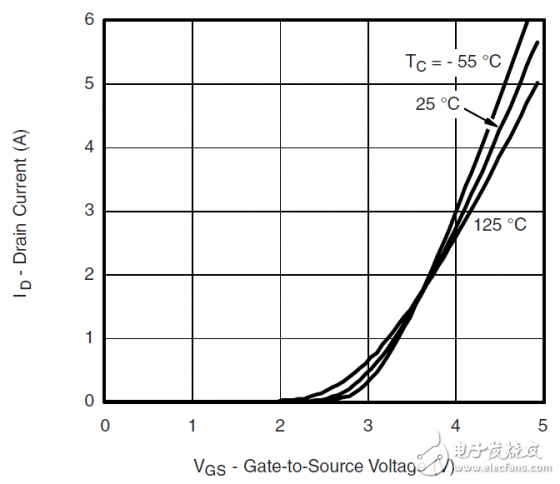

实际测试时,一件意想不到的事情发生了,TX_EN为逻辑0时,实际的电压值时0.7V,而这小小的0.7V竟然令Q7导通了,这与Si2309中所描述的天壤之别,如下图,当Vgs为0.7V时,Id应为0,Si2309应处于截止状态,而实际并非如此。

无奈之际,我想到了三极管,FMMT493TC是一颗用在TPS2379参考设计中的高压NPN三极管,其工作电压大于100V,Ic更可以达到1A,完全可以符合这个PIN Diode驱动电路的要求。如前所述,逻辑0是有0.7V左右的电压,如果直接加在FMMT493TC,一定会使其导通,于是采用分压的方法提供基极偏置电压。最终调整完成的原理图如下(其中No Load即为不贴装),经过长期测试,不再出现异常。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)